本帖最后由 machairodus 于 2014-5-28 19:51 编辑

小弟我最近用EDK做一个视频采集系统,做了一个视频采集的IP核,希望将采集

到的视频数据传到DDR2 中缓存。制作ip核时,我在IPIF界面选择使用rdpfifo,目的是

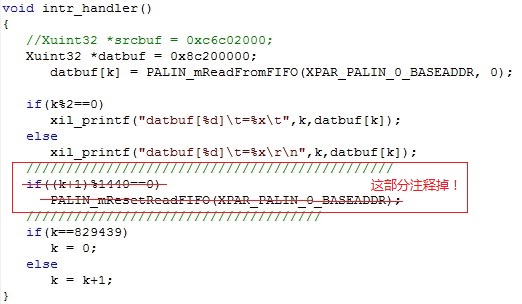

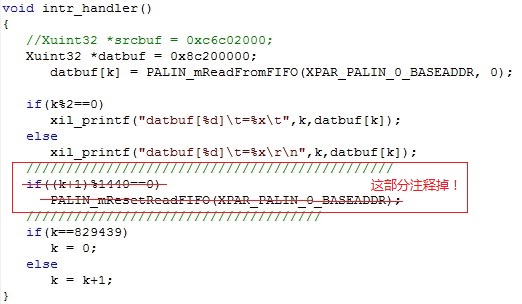

在userlogic中,将有效数据写入此fifo,然后在控制C程序中,使用生成的驱动函数:

PALIN_mReadFromFIFO(XPAR_PALIN_0_BASEADDR,0)来将数据写入DDR2中。下图

就是利用中断从FIFO中读取数据写入DDR的过程。

然后问题就出现了,我发现写入DDR2中的数据只有前2048个是正确的,后面的都

不对,而2048正好是我设定的FIFO深度,所以问题应该是FIFO溢出了,我是这样理解的:

PALIN_mReadFromFIFO()这个函数虽然读出了fifo中的数据,但是并没有释放fifo的

空间,导致只能正确写入2048个数据,不知道我的理解对不对?

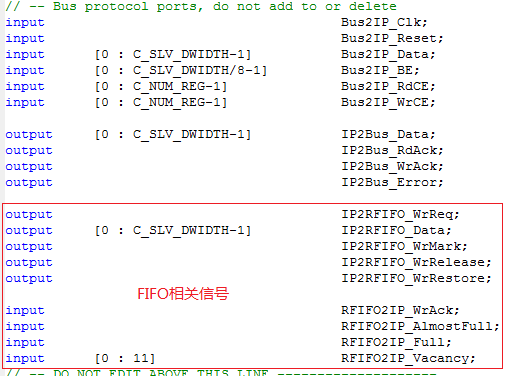

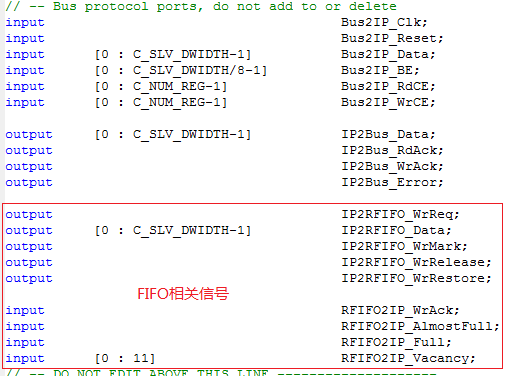

究竟要如何做才能保证fifo释放了呢?在userlogic中,关于此FIFO只给了下图中几个信号,

其中能操作的也就output那几个,而IP2FIFO_Release、IP2FIFO_Restore和IP2FIFO_WrMark

这三个信号是用于packet的,这里没用到也不管,那么就只剩下IP2FIFO_WrReq和IP2FIFO_Data

了,但是这两个信号是用来往fifo里写数据的。在这里似乎也不能释放fifo?

怎么样才能解决fifo溢出的问题呢?希望各位大牛们能解决我的困惑!或者给我指一条其他的路,

只要能将数据正确写入DDR2中就行。谢谢了!

小弟我最近用EDK做一个视频采集系统,做了一个视频采集的IP核,希望将采集

到的视频数据传到DDR2 中缓存。制作ip核时,我在IPIF界面选择使用rdpfifo,目的是

在userlogic中,将有效数据写入此fifo,然后在控制C程序中,使用生成的驱动函数:

PALIN_mReadFromFIFO(XPAR_PALIN_0_BASEADDR,0)来将数据写入DDR2中。下图

就是利用中断从FIFO中读取数据写入DDR的过程。

然后问题就出现了,我发现写入DDR2中的数据只有前2048个是正确的,后面的都

不对,而2048正好是我设定的FIFO深度,所以问题应该是FIFO溢出了,我是这样理解的:

PALIN_mReadFromFIFO()这个函数虽然读出了fifo中的数据,但是并没有释放fifo的

空间,导致只能正确写入2048个数据,不知道我的理解对不对?

究竟要如何做才能保证fifo释放了呢?在userlogic中,关于此FIFO只给了下图中几个信号,

其中能操作的也就output那几个,而IP2FIFO_Release、IP2FIFO_Restore和IP2FIFO_WrMark

这三个信号是用于packet的,这里没用到也不管,那么就只剩下IP2FIFO_WrReq和IP2FIFO_Data

了,但是这两个信号是用来往fifo里写数据的。在这里似乎也不能释放fifo?

怎么样才能解决fifo溢出的问题呢?希望各位大牛们能解决我的困惑!或者给我指一条其他的路,

只要能将数据正确写入DDR2中就行。谢谢了!

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

FIFO的位宽是默认的32位,而视频数据是8位,也就是说只用到了FIFO的高8位。我的问题主要是“已经通过驱动函数读出了FIFO中的2048个正确数据,但是FIFO却没有被释放,后续的数据不能写入FIFO。”

我的理解是这样的,因为这个fifo的作用是将IP核的数据通过microblaze写入DDR,所以写入fifo这部分功能应该是在IP中实现(也就是userlogic中),而读取fifo则应该是通过c程序(生成的驱动函数)实现。现在由于不知道如何在读取fifo中数据的同时释放fifo,导致只能正确执行fifo深度(2048)的读写操作。

恩,这里我觉得是用了FIFO的低8位,,同时write-->FIFO;IP 接口功能实现;

同时:read FIFO的数据,则是可以考虑 用相同的IP,,反过来读取,,看可以借鉴BRAM的方式不?个人见解,

等待高手

一周热门 更多>