本帖最后由 xiantingfeng 于 2014-3-7 22:17 编辑

Xilinx的ddr2 控制器出问题了,自己写的读写程序,很奇怪,读写256M的内存条,64位宽,突发长度为8。

设起始写地址为1,存连续的整数,如果读地址为1的话,读写的数据一样。

如果读地址为2,出现后面这种情况,2,3,1,4,6,7,8,5 。

如果起始地址为3,读的数据为3,4,1,2,7,8,5,6 。

是不是读写程序出问题了,求解。

N取32,burst_cnt,burst_cnt2 是存储的计数,wr_state是写数据的状态机,write_flag是(app_wdf_afull == 1) || (app_af_afull == 1)后中止写的标志位。写这些数据的时候,write_flag一直有效。

求解!

部分程序如下:

if (burst_cnt2 < N+1) begin

if (burst_cnt < N+1) begin

if (write_flag == 1) begin

if ((ram3_cnt != N+1) && (ram3_cnt != N+2)) begin

ram3_cnt <= ram3_cnt + 2;

app_af_cmd <= 3'b000; app_wdf_wren <= 1;

wr_data_rise <= ram3_cnt + j_mti_N; wr_data_fall <= ram3_cnt+1 + j_mti_N;

case(wr_state)

1: begin app_af_wren <= 1; wr_state <= 2;

if (burst_cnt == 1)

app_af_addr <= 5242880 +1+{burst_cnt2,10'b0}-1024;

else app_af_addr <= app_af_addr + 8; end

2: begin app_af_wren <= 0; wr_state <= 3; end

3: wr_state <= 4;

4: begin wr_state <= 1; burst_cnt <= burst_cnt + 8;

if ((app_wdf_afull == 1) || (app_af_afull == 1)) begin

write_flag <= 0; // app_wdf_wren <= 0; app_af_wren <= 0;

end end

endcase

end

end

else begin

app_wdf_wren <= 0; app_af_wren <= 0;

if ((app_wdf_afull == 0) && (app_af_afull == 0)) begin

write_flag <= 1; wr_state <= 1; //wr_state <= state1;

end

end

end

else begin

app_wdf_wren <= 0; app_af_wren <= 0;

burst_cnt2 <= burst_cnt2 + 1;

j_mti_N <= j_mti_N + 1024;//100;

burst_cnt <= 1; ram3_cnt <= 1;

end

end

else begin

if (app_af_afull==0) begin

if (burst_cnt3 < N+1)

if (burst_cnt3 == 1)

app_af_addr <= 5242880 +1;

else

app_af_addr <= app_af_addr + 8;

app_af_cmd <= 3'b001; app_af_wren <= 1;

burst_cnt3 <= burst_cnt3 + 8;

end

end

end

Xilinx的ddr2 控制器出问题了,自己写的读写程序,很奇怪,读写256M的内存条,64位宽,突发长度为8。

设起始写地址为1,存连续的整数,如果读地址为1的话,读写的数据一样。

如果读地址为2,出现后面这种情况,2,3,1,4,6,7,8,5 。

如果起始地址为3,读的数据为3,4,1,2,7,8,5,6 。

是不是读写程序出问题了,求解。

N取32,burst_cnt,burst_cnt2 是存储的计数,wr_state是写数据的状态机,write_flag是(app_wdf_afull == 1) || (app_af_afull == 1)后中止写的标志位。写这些数据的时候,write_flag一直有效。

求解!

部分程序如下:

if (burst_cnt2 < N+1) begin

if (burst_cnt < N+1) begin

if (write_flag == 1) begin

if ((ram3_cnt != N+1) && (ram3_cnt != N+2)) begin

ram3_cnt <= ram3_cnt + 2;

app_af_cmd <= 3'b000; app_wdf_wren <= 1;

wr_data_rise <= ram3_cnt + j_mti_N; wr_data_fall <= ram3_cnt+1 + j_mti_N;

case(wr_state)

1: begin app_af_wren <= 1; wr_state <= 2;

if (burst_cnt == 1)

app_af_addr <= 5242880 +1+{burst_cnt2,10'b0}-1024;

else app_af_addr <= app_af_addr + 8; end

2: begin app_af_wren <= 0; wr_state <= 3; end

3: wr_state <= 4;

4: begin wr_state <= 1; burst_cnt <= burst_cnt + 8;

if ((app_wdf_afull == 1) || (app_af_afull == 1)) begin

write_flag <= 0; // app_wdf_wren <= 0; app_af_wren <= 0;

end end

endcase

end

end

else begin

app_wdf_wren <= 0; app_af_wren <= 0;

if ((app_wdf_afull == 0) && (app_af_afull == 0)) begin

write_flag <= 1; wr_state <= 1; //wr_state <= state1;

end

end

end

else begin

app_wdf_wren <= 0; app_af_wren <= 0;

burst_cnt2 <= burst_cnt2 + 1;

j_mti_N <= j_mti_N + 1024;//100;

burst_cnt <= 1; ram3_cnt <= 1;

end

end

else begin

if (app_af_afull==0) begin

if (burst_cnt3 < N+1)

if (burst_cnt3 == 1)

app_af_addr <= 5242880 +1;

else

app_af_addr <= app_af_addr + 8;

app_af_cmd <= 3'b001; app_af_wren <= 1;

burst_cnt3 <= burst_cnt3 + 8;

end

end

end

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

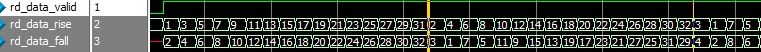

读地址低三位最好为0,不是任意地址开始的,读数据就是地址随后的8个数据,你可以上Xilinx的网站,搜Reading data is disordered when using ddr2 controller,这个是我提的问题,解决了。

rise和fall是实际写入的数据。

valid为低,out有输出,我在modelsim仿真中也看得,这个没影响,你可以用valid作为判断条件接收输出数据,要想弄清原因,可以看model.v文件。

一周热门 更多>