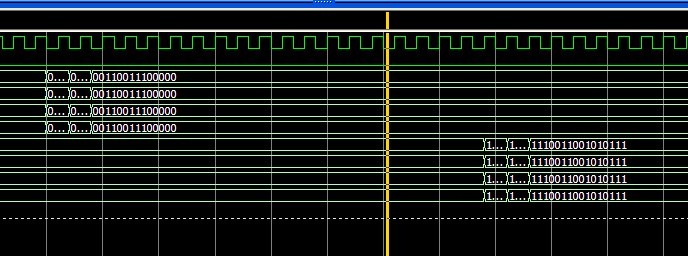

如下图所示,程序例化了四个模块,使用的同一个IP,数据要求是流水线输入流水线输出。功能仿真时,输出功能正确。但是后仿真时,有的输出无法在同一个周期内稳定,而且,四个相同的模块输出结果还不一样,后仿真中输出只有第一个正常。时序约束中只设置的时钟周期,4ns,静态时序报告显示如下:

Clock to Setup on destination clock clk

---------------+---------+---------+---------+---------+

| Src:Rise| Src:Fall| Src:Rise| Src:Fall|

Source Clock |Dest:Rise|Dest:Rise|Dest:Fall|Dest:Fall|

---------------+---------+---------+---------+---------+

clk | 3.962| | | |

---------------+---------+---------+---------+---------+

Timing summary:

---------------

Timing errors: 0 Score: 0 (Setup/Max: 0, Hold: 0)

Constraints cover 253308 paths, 0 nets, and 25468 connections

Design statistics:

Minimum period: 3.962ns{1} (Maximum frequency: 252.398MHz)

请大侠分析下原因,指导下小弟。

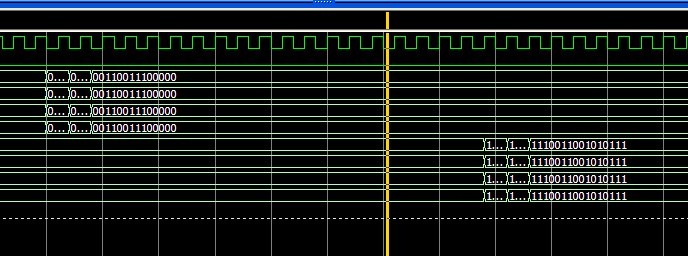

前仿真

后仿真

Clock to Setup on destination clock clk

---------------+---------+---------+---------+---------+

| Src:Rise| Src:Fall| Src:Rise| Src:Fall|

Source Clock |Dest:Rise|Dest:Rise|Dest:Fall|Dest:Fall|

---------------+---------+---------+---------+---------+

clk | 3.962| | | |

---------------+---------+---------+---------+---------+

Timing summary:

---------------

Timing errors: 0 Score: 0 (Setup/Max: 0, Hold: 0)

Constraints cover 253308 paths, 0 nets, and 25468 connections

Design statistics:

Minimum period: 3.962ns{1} (Maximum frequency: 252.398MHz)

请大侠分析下原因,指导下小弟。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

你指的是时序报告给出的时序不可靠吗?我后仿真只能测试到180MHz频率左右,达不到250MHz。

后仿真只测到180HMz频率左右,离临界点的频率还有点远啊。。

一周热门 更多>