ERROR:NgdBuild:1424 - part supplied at commandline 'xc6slx100t-fgg676-3' using

'-p' and specified through 'CONFIG PART' constraint 'XC6SLX45T-FGG484-3'

should not differ

ERROR:ConstraintSystem:59 - Constraint <NET "phy_4x_ser_clk/UCLK" TNM_NET =

"UCLK";> [srio_v5_6/example_design/srio_v5_6_top.ucf(82)]: NET

"phy_4x_ser_clk/UCLK" not found. Please verify that:

1. The specified design element actually exists in the original design.

2. The specified object is spelled correctly in the constraint source file.

ERROR:ConstraintSystem:59 - Constraint <NET "phy_4x_ser_clk/UCLK2" TNM_NET =

"UCLK2";> [srio_v5_6/example_design/srio_v5_6_top.ucf(83)]: NET

"phy_4x_ser_clk/UCLK2" not found. Please verify that:

1. The specified design element actually exists in the original design.

2. The specified object is spelled correctly in the constraint source file.

ERROR:ConstraintSystem:59 - Constraint <NET "phy_4x_ser_clk/UCLK_DV4" TNM_NET =

"UCLK_DV4";> [srio_v5_6/example_design/srio_v5_6_top.ucf(84)]: NET

"phy_4x_ser_clk/UCLK_DV4" not found. Please verify that:

1. The specified design element actually exists in the original design.

2. The specified object is spelled correctly in the constraint source file.

ERROR:NgdBuild:604 - logical block 'srio_icon_gen.i_srio_icon' with type

'srio_icon' could not be resolved. A pin name misspelling can cause this, a

missing edif or ngc file, case mismatch between the block name and the edif

or ngc file name, or the misspelling of a type name. Symbol 'srio_icon' is

not supported in target 'spartan6'.

ERROR:NgdBuild:604 - logical block 'rio_de_wrapper/rio_ila1_gen.i_rio_ila' with

type 'rio_ila' could not be resolved. A pin name misspelling can cause this,

a missing edif or ngc file, case mismatch between the block name and the edif

or ngc file name, or the misspelling of a type name. Symbol 'rio_ila' is not

supported in target 'spartan6'.

ERROR:NgdBuild:604 - logical block

'rio_de_wrapper/phy_wrapper/srio_ila2_gen.i_phy_ila' with type 'phy_ila'

could not be resolved. A pin name misspelling can cause this, a missing edif

or ngc file, case mismatch between the block name and the edif or ngc file

name, or the misspelling of a type name. Symbol 'phy_ila' is not supported in

target 'spartan6'.

ERROR:NgdBuild:604 - logical block

'user_top/initiator_user/tickler/srio_vio_gen.i_srio_vio' with type

'srio_vio' could not be resolved. A pin name misspelling can cause this, a

missing edif or ngc file, case mismatch between the block name and the edif

or ngc file name, or the misspelling of a type name. Symbol 'srio_vio' is not

supported in target 'spartan6'.

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

什么pn是指引脚吗?刚看到文档,要修改ucf文件,是不是只要修改ucf文件即可,需不需要从新生成chipscope ip核?

进行chipscope调试 是不是先要添加CDC文件?

怎么用xco重新生成核?

phy_1x_ser_clk/u_refclk_ibufds_ML_BUFDS of type BUFDS for the following

reason.

The reason for this issue:

Some of the logic associated with this structure is locked. This should cause

the rest of the logic to be locked. A problem was found where we should

place BUFDS phy_1x_ser_clk/u_refclk_ibufds_ML_BUFDS off the edge of the chip

in order to satisfy the relative placement requirement of this logic. The

following components are part of this structure:

ERROR:Place:1073 - Placer was unable to create RPM[BUFDS_RPMs] for the component

phy_1x_ser_clk/u_refclk_ibufds_ML_BUFDS of type BUFDS for the following

reason.

The reason for this issue:

Some of the logic associated with this structure is locked. This should cause

the rest of the logic to be locked.A problem was found at site IPAD_X0Y12

where we must place BUFDS phy_1x_ser_clk/u_refclk_ibufds_ML_BUFDS in order to

satisfy the relative placement requirements of this logic. IPAD sys_clkp

appears to already be placed there which makes this design unplaceable. The

following components are part of this structure:

ERROR:Pack:1654 - The timing-driven placement phase encountered an error.

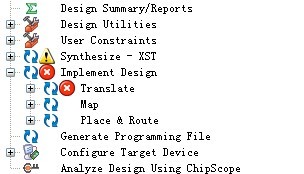

重新生成了,但map时出现上面错误。

一周热门 更多>