本帖最后由 elcfoucs 于 2013-11-18 13:57 编辑

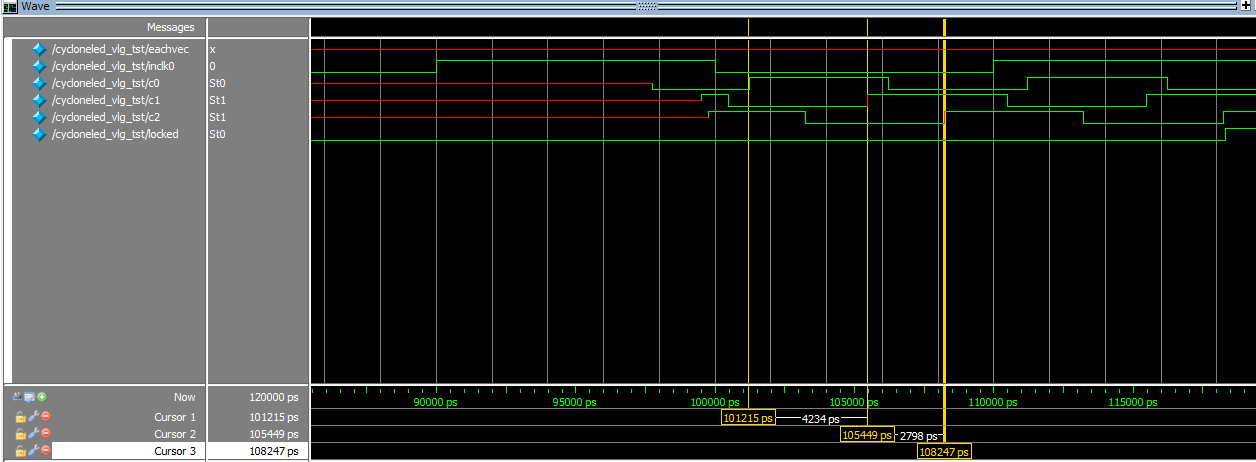

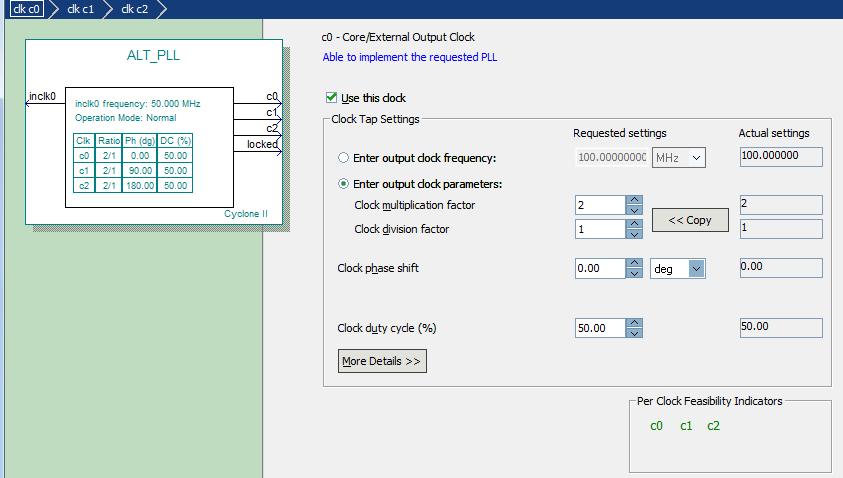

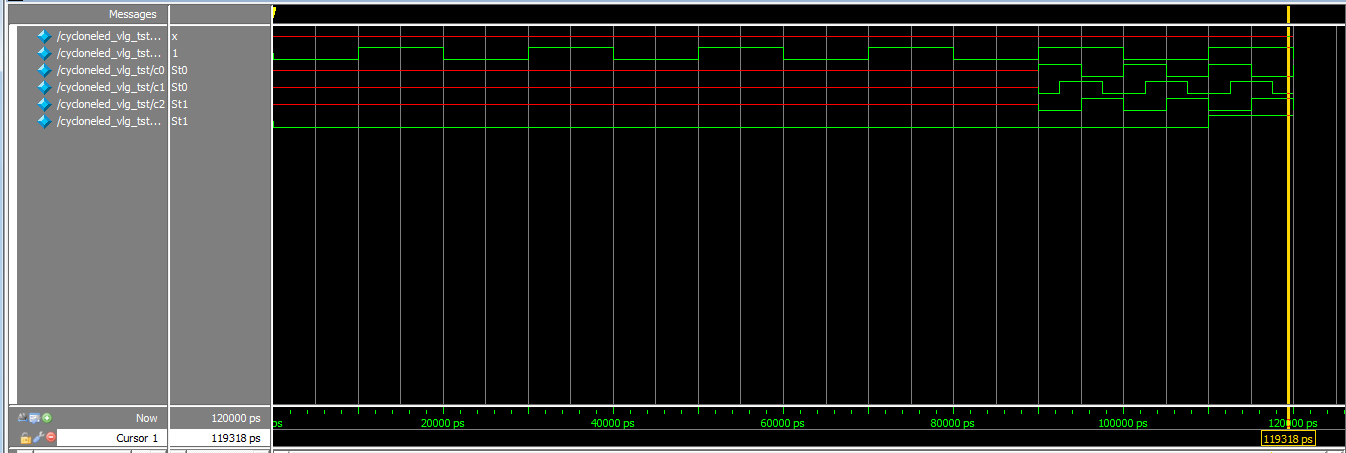

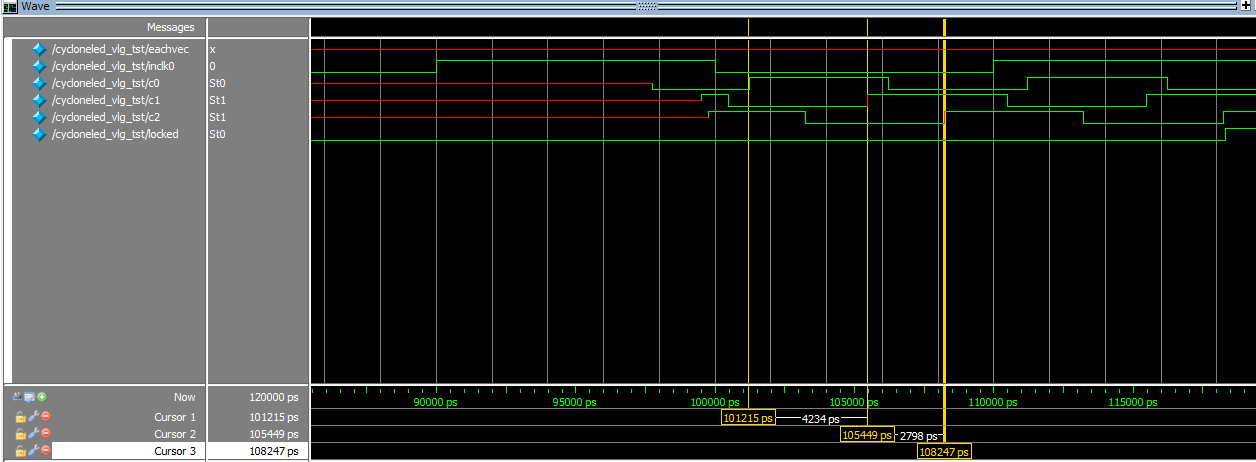

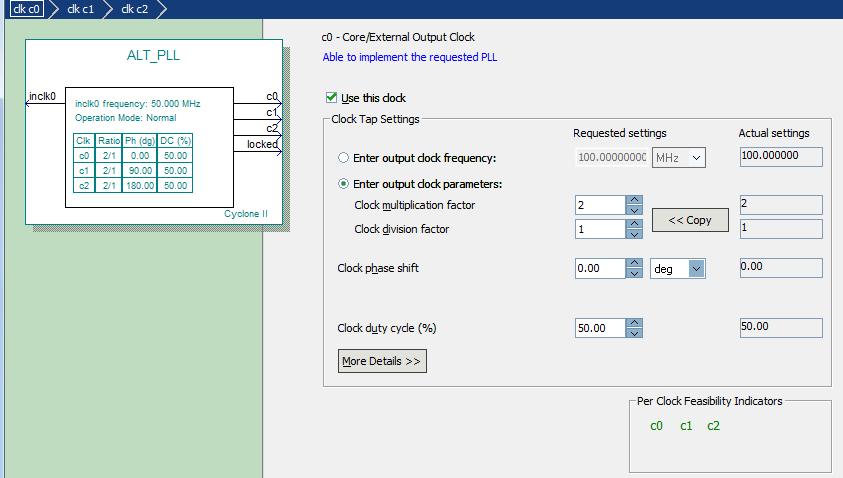

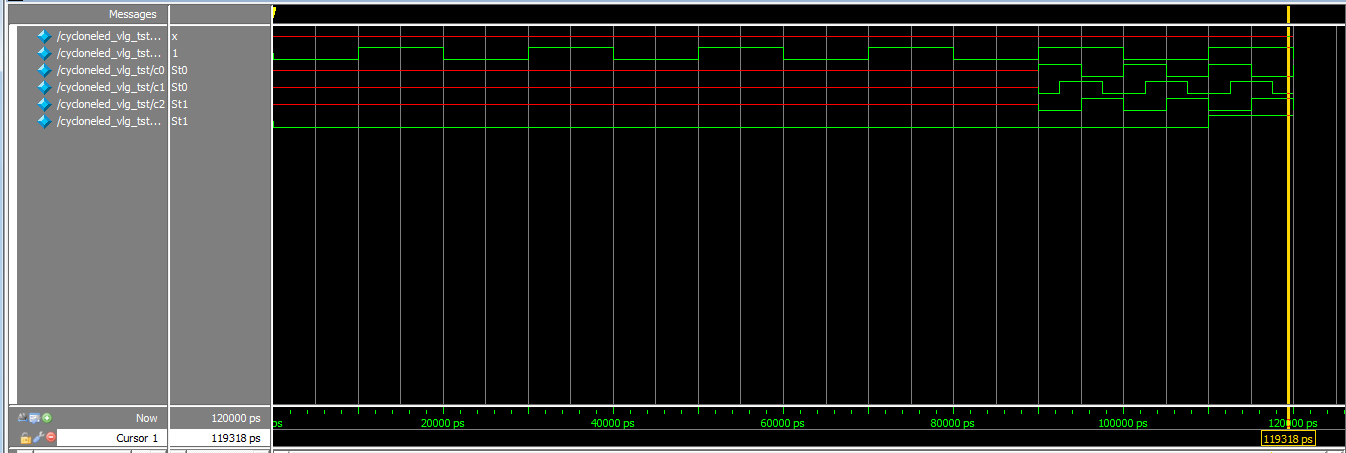

我使用megawizard生成PLL,外部50M,生成3个依次延迟90度的100M时钟,C0 0度, C1 90度 ,C2 180度,然后使用modelsim 门级仿真,出来的结果不太对啊!不应该是依次延迟1/100M/4么?RTL级仿真是对的。。这该如何解决。。再调那个相位值?

我使用megawizard生成PLL,外部50M,生成3个依次延迟90度的100M时钟,C0 0度, C1 90度 ,C2 180度,然后使用modelsim 门级仿真,出来的结果不太对啊!不应该是依次延迟1/100M/4么?RTL级仿真是对的。。这该如何解决。。再调那个相位值?

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>