本帖最后由 asdf012 于 2013-9-29 21:21 编辑

求助:ddr2 ram,256M,64位位宽,突发长度为4时,读写地址如何提供。

1. 提供给控制器的数据是上升沿和下降沿的拼接,一个周期提供两个数据到app_wdf_data,位宽为128位。那么写的地址该如何产生给app_af_addr?

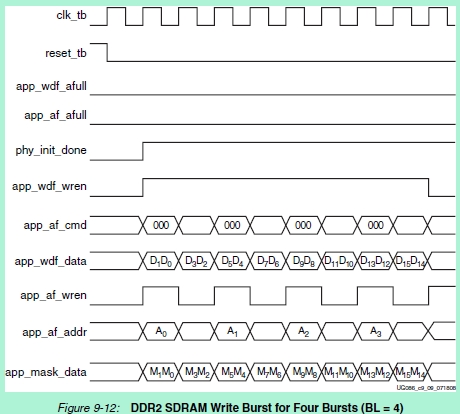

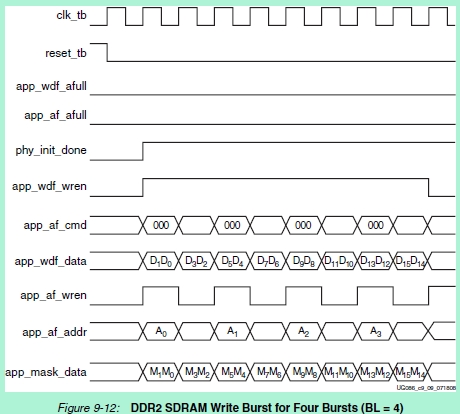

2. ddr2的ug086文档中ddr2的突发长度为4时,时序图为什么是下面这样。

app_wdf_data 赋值从D0到 D15,app_af_wren,为1和0交替出现,地址给A0~A4。是不是D0~D3为一个突发读写?D0~D3一个cmd命令即可?D3D2时wren=0 cmd未标值,作何解。

突发长度为8时,是不是第一个周期给cmd,wren=1即可?

如果app_wdf_afull, app_af_afull 为0,下一次突发写是不是 能立即进行?比如假设D0~D3为一个突发,example design的ug086说明中说,burst为4时两个写命令。

3. 突发读写是不是给起始地址即可,地址为接下来的连续地址?能不能读写不连续的地址?

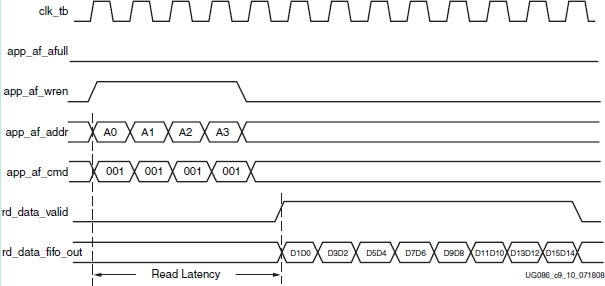

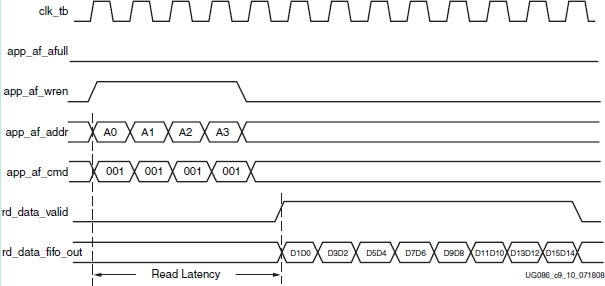

4. 读数据时序图连续给了A0~A3四个地址,rd_data_valid 后,D0~D16,是不是就对应4个突发读?

5. mask_data是数据屏蔽的吧,不用时怎么处理,看到有的代码中赋值为0,是不是这样就可以还是不用给输入。

ddr2看了半个月以上了,还是不太清楚,求助啊。

求助:ddr2 ram,256M,64位位宽,突发长度为4时,读写地址如何提供。

1. 提供给控制器的数据是上升沿和下降沿的拼接,一个周期提供两个数据到app_wdf_data,位宽为128位。那么写的地址该如何产生给app_af_addr?

2. ddr2的ug086文档中ddr2的突发长度为4时,时序图为什么是下面这样。

app_wdf_data 赋值从D0到 D15,app_af_wren,为1和0交替出现,地址给A0~A4。是不是D0~D3为一个突发读写?D0~D3一个cmd命令即可?D3D2时wren=0 cmd未标值,作何解。

突发长度为8时,是不是第一个周期给cmd,wren=1即可?

如果app_wdf_afull, app_af_afull 为0,下一次突发写是不是 能立即进行?比如假设D0~D3为一个突发,example design的ug086说明中说,burst为4时两个写命令。

3. 突发读写是不是给起始地址即可,地址为接下来的连续地址?能不能读写不连续的地址?

4. 读数据时序图连续给了A0~A3四个地址,rd_data_valid 后,D0~D16,是不是就对应4个突发读?

5. mask_data是数据屏蔽的吧,不用时怎么处理,看到有的代码中赋值为0,是不是这样就可以还是不用给输入。

ddr2看了半个月以上了,还是不太清楚,求助啊。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

数据屏蔽位就是屏蔽掉数据线上某一位数,你不用都给它置成“不屏蔽”,好像是0吧,不管它。

还有,我曾经用也是SP6,但用的是ise13.2,很多信号的命名和你的这个不一样啊。。。。反正,一切都在文档中,你自己慢慢琢磨吧

多谢你回复得这么详细。

ddr2的几十页英文文档看了几遍,有的还是没说清楚。根据文档和时序图相互推测,得出上面那些可能的答案,加上你这一说,现在基本清楚了。

谢谢!app_wdf_fifo的宽度是的,128位,通过对64位位数据的位拼接实现的。

想问下突发写长度为8,如果只修改一个数据,给出这个数据的地址,通过mask_data = 56是不是后面7个数据的写入就屏蔽掉了。mask_data 具体如何赋值?只知道文档上说位宽为8,屏蔽的是字节。

mask_data为0就好了

一周热门 更多>