本帖最后由 sen19890606 于 2013-9-3 13:55 编辑

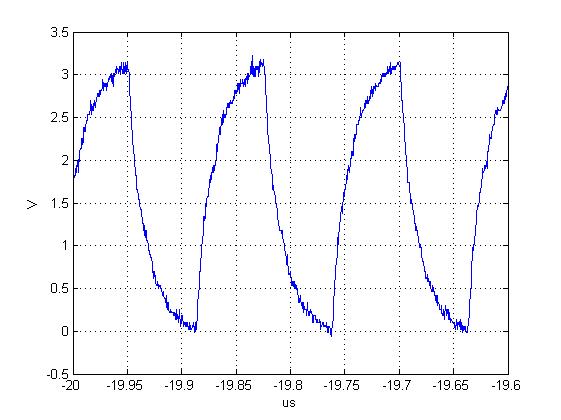

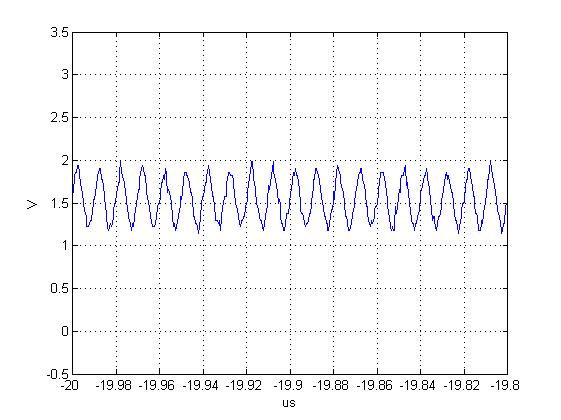

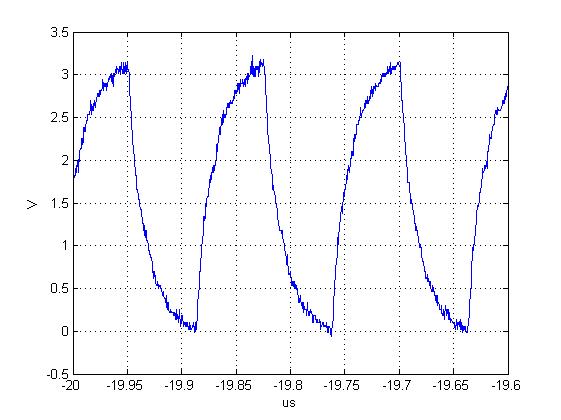

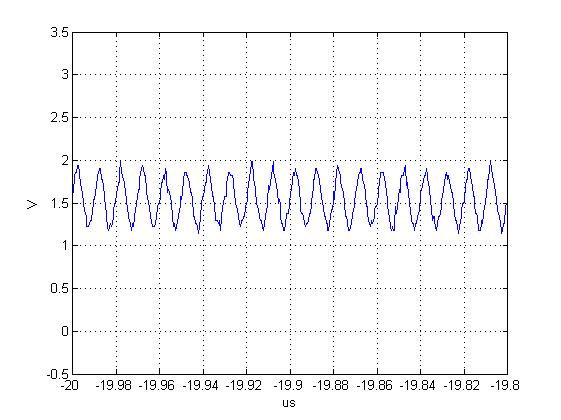

本人使用的是购买的核心板,cyclone IV芯片,想弄个引脚输出100MHz给DA芯片当时钟,选择3.3V电平标准,分别测试了8MHz和100MHz(直接将PLL输出接引脚),结果用示波器观察的波形是这样的,左图8MHz,右图100MHz

8MHz的还可以接受,100MHz的那个峰峰值也太小了吧,两个设置都是一样的,就是改了PLL的输出频率,而且我看了cyclone IV的数据手册,PLL外部时钟输出最高可达472.5MHz,我的这个不知什么原因,求指点啊

本人使用的是购买的核心板,cyclone IV芯片,想弄个引脚输出100MHz给DA芯片当时钟,选择3.3V电平标准,分别测试了8MHz和100MHz(直接将PLL输出接引脚),结果用示波器观察的波形是这样的,左图8MHz,右图100MHz

8MHz的还可以接受,100MHz的那个峰峰值也太小了吧,两个设置都是一样的,就是改了PLL的输出频率,而且我看了cyclone IV的数据手册,PLL外部时钟输出最高可达472.5MHz,我的这个不知什么原因,求指点啊

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

也就是说FPGA不能提供100MHz时钟是吗,但datasheet上说外部时钟输出最高472.5MHz是啥意思啊?

提供的pll在内部使用是没问题的,但是你用在了外部IO上就有问题

那括号里的external clock output是指什么啊,因为下面又给出了这个东西

这个应该是内部全局网络,在芯片内部用的吧

一周热门 更多>