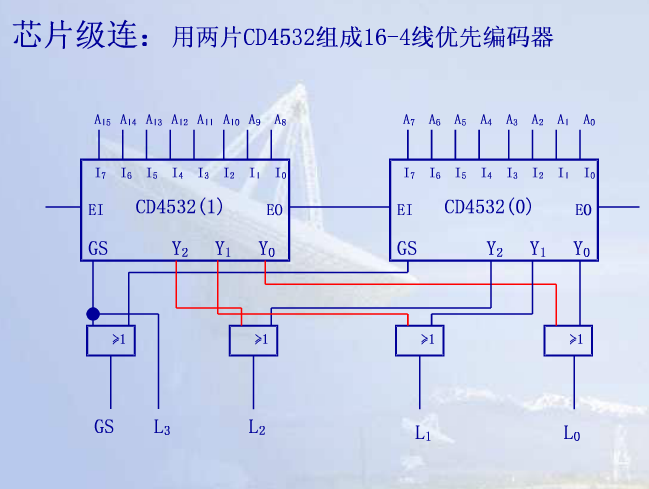

小弟想设计一个16-4编码器。单独的16-3编码器是没有问题的,16-4在调用底层原件端口映射时出现问题了。请大神分析。

1.16-3编码器

--3-8优先编码器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

--端口定义

entity sn74ls148 is

port(i:in std_logic_vector(7 downto 0);

ys:out std_logic;

yex:out std_logic;

q:out std_logic_vector(2 downto 0);

s:in std_logic);

end entity;

--结构体描述

architecture behave of sn74ls148 is

begin

ys<=not( not(s) and i(0) and i(1) and i(2) and i(3) and i(4) and i(5) and i(6) and i(7) );

yex<=(s or (i(0) and i(1) and i(2) and i(3) and i(4) and i(5) and i(6) and i(7) ));

process(s,i)

begin

if (s='0') then

if (i(7)='0') then

q<="111";

elsif (i(6)='0') then

q<="110";

elsif (i(5)='0') then

q<="101";

elsif (i(4)='0') then

q<="100";

elsif (i(3)='0') then

q<="011";

elsif (i(2)='0') then

q<="010";

elsif (i(1)='0') then

q<="001";

elsif (i(0)='0') then

q<="000";

else

q<="XXX";

end if;

end if;

end process;

end behave;

2.16-4编码器

--16-4优先编码器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

--端口定义

entity coder16_4 is

port(data_in:in std_logic_vector(15 downto 0);

data_out:out std_logic_vector(3 downto 0);

ys16_4:out std_logic;

yex16_4:out std_logic

);

end entity;

--结构体描述

architecture rtl of coder16_4 is

--此处为了和端口映射连接,定义了一些信号,有些糊涂

signal ys_temp:std_logic;

signal yex_temp:std_logic;

signal ys_temp1:std_logic:='0';

signal ys_temp2:std_logic;

signal yex_temp1:std_logic;

signal yex_temp2:std_logic;

signal b,c:std_logic_vector(7 downto 0);

signal d,e:std_logic_vector(2 downto 0);

component sn74ls148

port(i:in std_logic_vector(7 downto 0);

ys:out std_logic;

yex:out std_logic;

q:out std_logic_vector(2 downto 0);

s:in std_logic);

end component;

begin

process(s16_4,data_in)

begin

b<=i(7) and i(6) and i(5) and i(4) and i(3) and i(2) and i(1) and i(0) ;

c<=i(15) and i(14) and i(13) and i(12) and i(11) and i(10) and i(9) and i(8) ;

u1:sn74ls148 port map(i=>b,ys=>ys_temp,yex=>yex_temp,q=>d,s=>ys_temp1);

u2:sn74ls148 port map(i=>c,ys=>ys_temp,yex=>yex_temp1,q=>e,ys_temp1=>s;

data_out(3)<=not yex;

data_out(2)<=not (d(2) and e(2));

data_out(1)<=not (d(1) and e(1));

data_out(0)<=not (d(0) and e(0));

end process;

end rtl;

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

大神总是无语。

不知道怎么端口映射 ,自己写的编译不过

一周热门 更多>