小弟这些日子一直在捣鼓DDR2,现在在做DDR2的Modelsim 仿真,遇到了困难。

我将我的DDR2控制模块 都做成了原理图的形式。但是出问题了

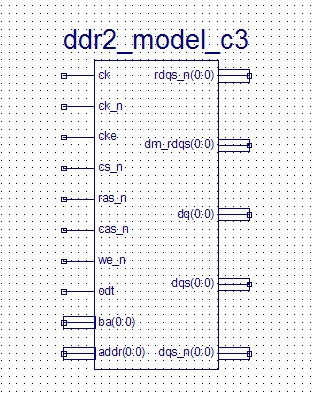

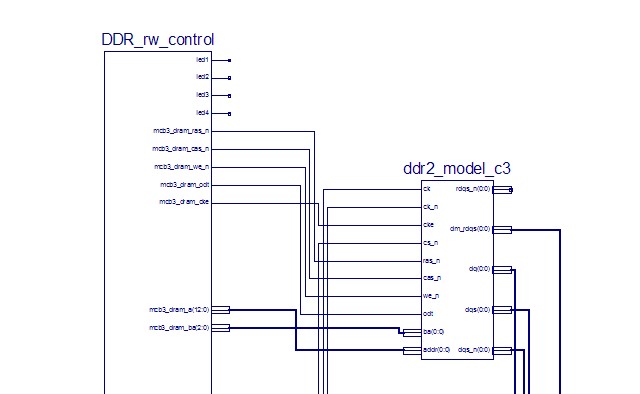

1.DDR2 模型生成的不正确。如果不把头文件包含进去,生成的DDR2 符号 中所有数据位宽都是0 如图

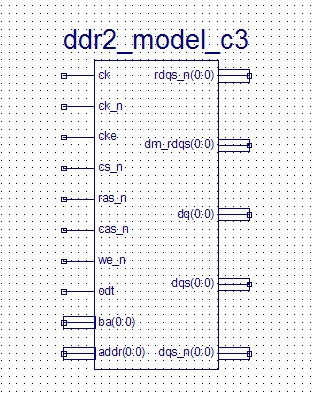

如果把头文件中的内容 复制到 ddr2_model_c3.v 文件中, 再生成symbol,数据位宽会加上,但是地址线 的位宽不对。

请问有朋友做过类似的DDR2 仿真的吗?我用的DDR2 是1Gbit 16位的 Micron的MT47H64M16.

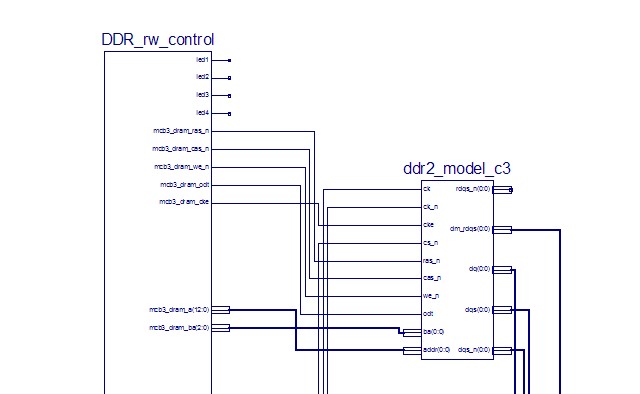

这是我的顶层原理图:(截图截不全)

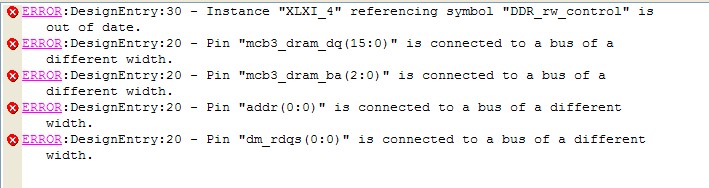

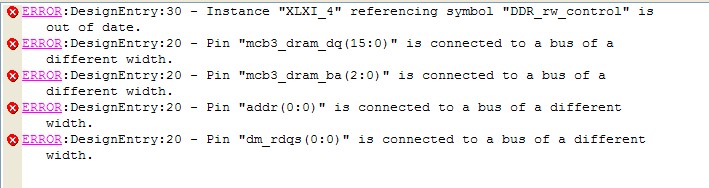

这样会报错: 第一个错误不明白,其余都是端口不匹配

恳请大神帮助啊!

我将我的DDR2控制模块 都做成了原理图的形式。但是出问题了

1.DDR2 模型生成的不正确。如果不把头文件包含进去,生成的DDR2 符号 中所有数据位宽都是0 如图

如果把头文件中的内容 复制到 ddr2_model_c3.v 文件中, 再生成symbol,数据位宽会加上,但是地址线 的位宽不对。

请问有朋友做过类似的DDR2 仿真的吗?我用的DDR2 是1Gbit 16位的 Micron的MT47H64M16.

这是我的顶层原理图:(截图截不全)

这样会报错: 第一个错误不明白,其余都是端口不匹配

恳请大神帮助啊!

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

刚开始用modelsim仿真时也是一只仿真不了,后来把“端口不匹配”的相关端口在ddr2_model.v中重新定义了一下(直接用localparameter)直接用ISIM仿真就通过了,另外用modelsim仿真时,头文件需要用全路径,例如`include "F:/ise/myddr123/ipcore_dir/myddr2/example_design/rtl/myddr2_parameters_0.v" 如果还不行的话 将路径中的“/”换成“”试下 希望可以帮到你 呵呵

感谢啊

谢谢你!我再试一下。我现在直接用chipescope 去看信号了,modelsim 仿真起来好卡,占内存太大了。以后多交流!

谢谢!还有个问题我在chipescope ILA 中加入 DCM 输出的时钟信号,为啥 MAP 时就会报错?

Place:1136 - This design contains a global buffer instance,

<XLXI_5/clkout1_buf>, driving the net, <XLXN_2>, that is driving the

following (first 30) non-clock source pins.

< PIN: U_ila_pro_0/U0/I_TQ3.G_TW[0].U_TQ.D; >

This is not a recommended design practice in Spartan-6 due to limitations in

the global routing that may cause excessive delay, skew or unroutable

situations. It is recommended to only use a BUFG resource to drive clock

loads. If you wish to override this recommendation, you may use the

CLOCK_DEDICATED_ROUTE constraint (given below) in the .ucf file to demote

this message to a WARNING and allow your design to continue.

< PIN "XLXI_5/clkout1_buf.O" CLOCK_DEDICATED_ROUTE = FALSE; >

而且即便 在ucf 中按照它的提示 设这 成FALSE, 发现抓取的信号 也不对,

是不是不能观察时钟信号?

看你用多大的时钟抓了 如果用低频率的时钟抓高频率的时钟(比如用100M的时钟或者小于100M的时钟抓取100M的时钟,这个是抓不住的 因为用<=100M的时钟抓的话 抓到全是1或者0) 所以抓的话用一个高频的时钟去抓 比如用200M去抓100M是可以抓住的

一周热门 更多>