本帖最后由 SuperX-man 于 2012-6-27 16:33 编辑

最近公司在做Planahead的xilinx大学计划部的材料更新工作,本版有幸能够更进一步接触Planahead工具,之前一直听说PlanAhead拥有强大的设计环境和分析工具,提供了一个按钮式的RTL到比特流(RTL-to- bitstream)的设计流程,该流程拥有全新的、增强的用户界面和项目管理功能。此外,通过布局规划、运行多种不同实现策略,图形化浏览层层次结构,快速时序分析,以及基于模块的实现方式,让客户最大限度地利用有限的时间和设计资源实现最大的生产(嘿嘿,这些都是官方的客套话,但对Planahead有了一个总体的描述)。

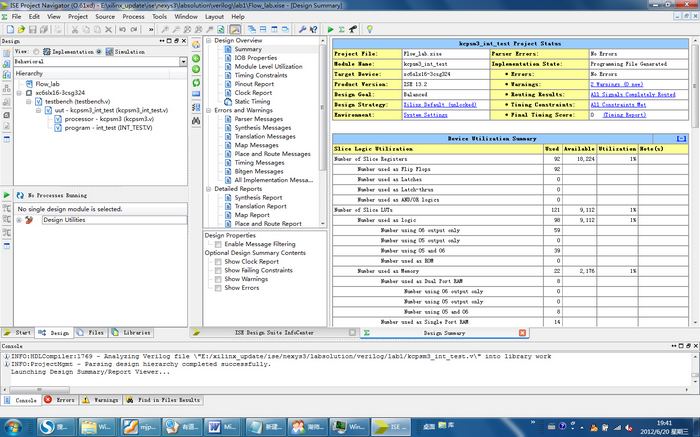

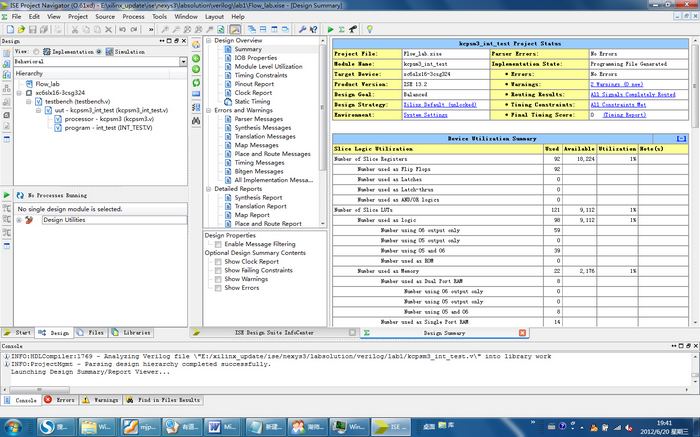

客套话先不说了,但用Planahead来做设计是个大体的趋势,先来个Planahead和ISE总体预览对比,待对Planahead有了总体的了解后,我们再详细的分析Planahead的性能与优越性。下面的截图的有各种软件的版本,有的是13.3、有的13.2,部分是14.1的,还有14.2的(内侧版哦),由于工作需要啊,只有混版本了,同时多版本的对比也有利于对软件的了解,截图的版本如果未标出,那截图图片的标头上会有版本信息,将在XILINX的每个大版本视图框架基本一样的,但万变不离其中,了解了一版,其他的也差不多了。

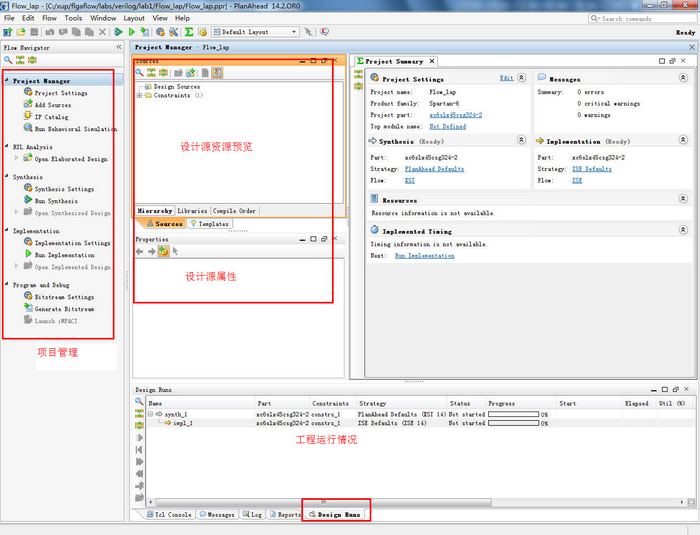

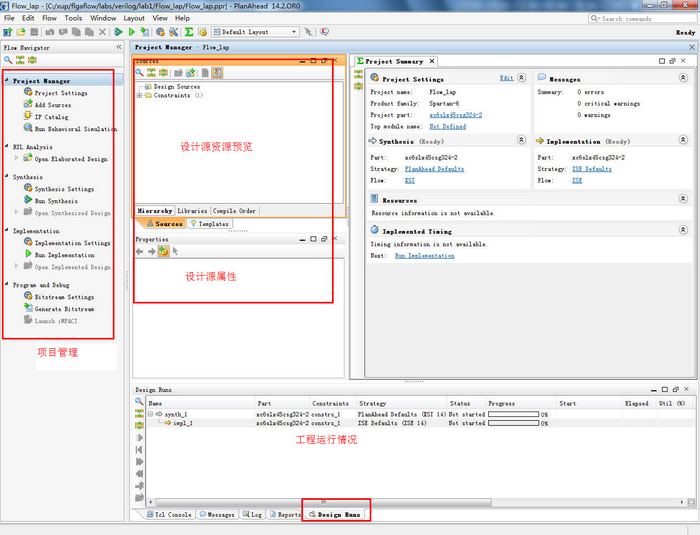

从图中可以看出(图中红 {MOD}表示变化较大部分),Planahead的左侧项目管理栏变化比较大,并强调和增加了设计源预览和属性两栏。通过点击Planahead项目管理栏里的操作可以完成整个项目的编译、布局布线工作,这个与ISE的Process一栏没有什么区别,但细心的读者会发现Planahead多了Open Synthesis/Implementation Design

的选项,我们点击Open Synthesis这个,看看会发生什么。

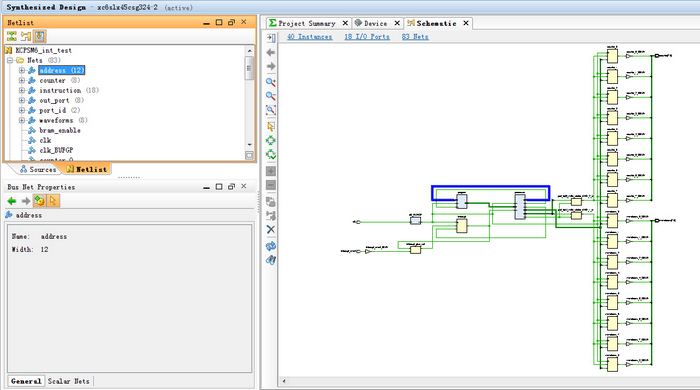

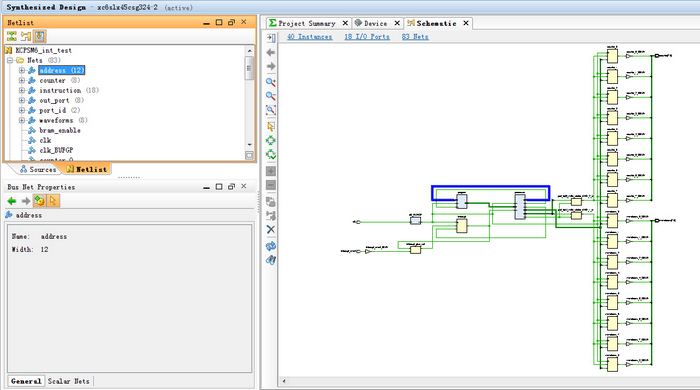

大家会看到Planahead会把生成设计的详细RTL预览,并提供连接和节点的属性及归类,让设计者对自己设计的电路有全局的认识,方便设计者优化设计与提高性能。这也体现了Planahead的设计理念——基于RTL到比特流(RTL-to- bitstream)的设计流程。当然如果你的设计不是很复杂,频率、性能要去不高,那你大可不必关着这些内容,使用傻瓜式一键操作,直接点击菜单栏下的的run implementation 或工程管理栏里的 绿 {MOD}按钮,就可完成从综合到布局布线的全部工作。

有了RTL预览之后,剩余的优化工作就好说了,在优化系统时,你可以看看到时是那一条路径的最大,那一条不合规矩,找到后以迅雷不及掩耳之势优化他,你就胜利了。

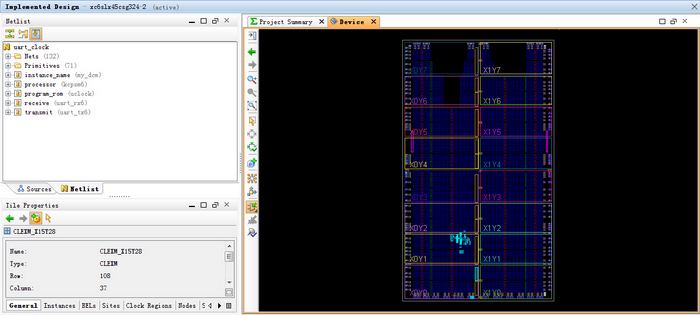

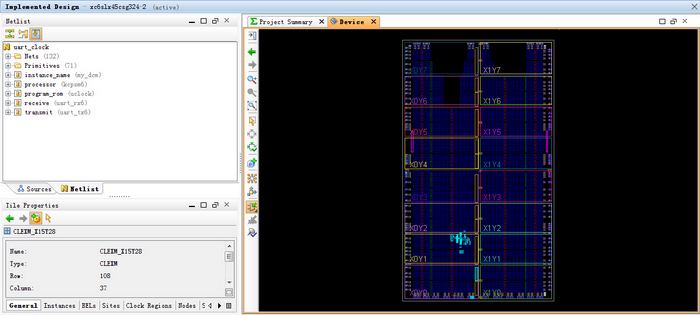

下面我们再看看点击Open Implementation Design,当然这一步必须是在你布局布线完成之后。这里我们可以关注的东西又多了一点,那就是已经可以看到我们的设计具体在芯片内部的结构图了,这个ISE也可以通过调用FPGA Editor来实现,但不及Planahead来的方便与直接啊。从这里我们可以大致的了解到选用芯片的内部资源以及资源的使用情况,并通过设计的大致位置情况判断设计的性能。图中荧光 {MOD}的斑点就是设计所使用的资源。我么来放大一下,再放大一下,可以看得很清楚了,就是组成FPGA的SLICEM、SLICEX了。很神奇吧!

由于篇幅及水平原因,其他的变化就不一一列出了,强烈期待你们的补充!

最近公司在做Planahead的xilinx大学计划部的材料更新工作,本版有幸能够更进一步接触Planahead工具,之前一直听说PlanAhead拥有强大的设计环境和分析工具,提供了一个按钮式的RTL到比特流(RTL-to- bitstream)的设计流程,该流程拥有全新的、增强的用户界面和项目管理功能。此外,通过布局规划、运行多种不同实现策略,图形化浏览层层次结构,快速时序分析,以及基于模块的实现方式,让客户最大限度地利用有限的时间和设计资源实现最大的生产(嘿嘿,这些都是官方的客套话,但对Planahead有了一个总体的描述)。

客套话先不说了,但用Planahead来做设计是个大体的趋势,先来个Planahead和ISE总体预览对比,待对Planahead有了总体的了解后,我们再详细的分析Planahead的性能与优越性。下面的截图的有各种软件的版本,有的是13.3、有的13.2,部分是14.1的,还有14.2的(内侧版哦),由于工作需要啊,只有混版本了,同时多版本的对比也有利于对软件的了解,截图的版本如果未标出,那截图图片的标头上会有版本信息,将在XILINX的每个大版本视图框架基本一样的,但万变不离其中,了解了一版,其他的也差不多了。

从图中可以看出(图中红 {MOD}表示变化较大部分),Planahead的左侧项目管理栏变化比较大,并强调和增加了设计源预览和属性两栏。通过点击Planahead项目管理栏里的操作可以完成整个项目的编译、布局布线工作,这个与ISE的Process一栏没有什么区别,但细心的读者会发现Planahead多了Open Synthesis/Implementation Design

的选项,我们点击Open Synthesis这个,看看会发生什么。

大家会看到Planahead会把生成设计的详细RTL预览,并提供连接和节点的属性及归类,让设计者对自己设计的电路有全局的认识,方便设计者优化设计与提高性能。这也体现了Planahead的设计理念——基于RTL到比特流(RTL-to- bitstream)的设计流程。当然如果你的设计不是很复杂,频率、性能要去不高,那你大可不必关着这些内容,使用傻瓜式一键操作,直接点击菜单栏下的的run implementation 或工程管理栏里的 绿 {MOD}按钮,就可完成从综合到布局布线的全部工作。

有了RTL预览之后,剩余的优化工作就好说了,在优化系统时,你可以看看到时是那一条路径的最大,那一条不合规矩,找到后以迅雷不及掩耳之势优化他,你就胜利了。

下面我们再看看点击Open Implementation Design,当然这一步必须是在你布局布线完成之后。这里我们可以关注的东西又多了一点,那就是已经可以看到我们的设计具体在芯片内部的结构图了,这个ISE也可以通过调用FPGA Editor来实现,但不及Planahead来的方便与直接啊。从这里我们可以大致的了解到选用芯片的内部资源以及资源的使用情况,并通过设计的大致位置情况判断设计的性能。图中荧光 {MOD}的斑点就是设计所使用的资源。我么来放大一下,再放大一下,可以看得很清楚了,就是组成FPGA的SLICEM、SLICEX了。很神奇吧!

由于篇幅及水平原因,其他的变化就不一一列出了,强烈期待你们的补充!

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

趋势面前,得加紧学习

相对于ISE,Planahead更多的是从理念和界面上首先进行比较大的改动,同一个界面可以很简单的完成设计,也可以完成更深层次的优化,工具还是那几个工具!

一周热门 更多>