2021-07-11 09:25发布

请教各位网友,我们用芯片进行ADC采样时误差是如何产生的,怎么做提高ADC采样精度?

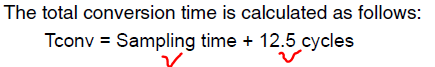

STM32家族中的所有芯片都内置了逐次逼近寄存器型ADC模块.内部大致框架如下:每次ADC转换先进行采样保持,然后分多步执行比较输出,步数等于ADC的位数,每个ADC时钟产生一个数据位。说到这里,用过STM32 ADC的人是不是想到了参考手册中关于12位ADC转换时间的公式:

ST官方就如何保障或改善ADC精度写了一篇应用笔记AN2834。该应用笔记旨在帮助用户了解ADC误差的产生以及如何提高ADC的精度。主要介绍了与ADC设计的相关内容,比如外部硬件设计参数,不同类型的ADC误差来源分析等,并提出了一些如何减小误差的设计上建议。这里我摘取部分内容,结合个人的理解加以整理与大家分享。更多细节可以去搜索AN2834下载细看。当我们在做STM32的ADC应用遇到转换结果不如意时,常有人提醒或建议你对采样时间或外部采样电路做调整。这里调整的最终目的就是让信号进入ADC模块的充电时间与内部采样时间匹配,保证采得的电压尽量真实,最终得到符合精度要求的转换结果。下面就聊聊相关话题。一、模拟信号源阻抗的影响

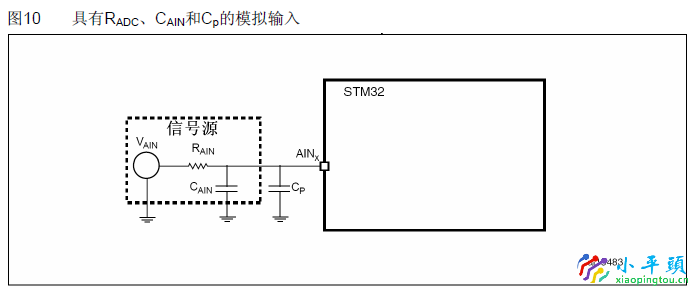

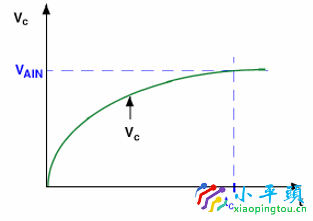

在做ADC操作时,在信号源与ADC引脚之间,或者说在串行电阻RAIN与ADC引脚AIN之间总有电流流过,自然会产生压降。内部采样电容CADC的充电由阻容网络中的开关和RADC控制。显然,对CADC有效的充电由【RADC RAIN】控制,充电时间常数是tc = (RADC RAIN) ×CADC。不难理解如果采样时间小于CADC通过RADC RAIN充电的时间,即ts < tc>可以看出,随着电阻(RADC RAIN)的增加,对保持电容的充电时间也需要相应增加。对于STM32而言,RADC是内部的采样开关电阻,阻值相对固定,具体数值在芯片的数据手册里有给出。所以,这里真正可能变动的电阻就是信号源电阻RAIN了,它的变化影响充电常数,进而影响到芯片内部采样时间的选择。注:tc是电容CADC充电完全的时间,此时Vc = VAIN(最大1/2LSB 误差)Vc:采样电容CADC上的电压tc = (RADC RAIN) × CADC 【CADC的值也是相对固定的】二、信号源的容抗与PCB分布电容的对ADC的影响做ADC时,除了考虑信号源端的电阻外,还需要考虑信号源本身容抗和在模拟输入端的分布电容(参见下图)。信号源的电阻和电容构成一个阻容网络,如果外部的电容(CAIN Cp)没能完全充电至输入信号电压,ADC转换的结果显然是不准确的。(CAIN Cp)的值越大,信号源的频率也就越受限制。(信号源上的外部电容和分布电容分别用CAIN和Cp表示。)

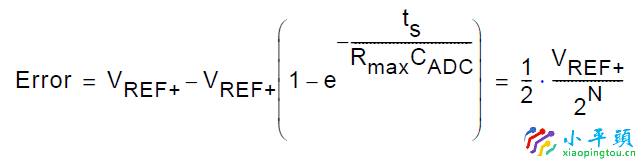

当外部电路的电容没有被模拟信号源完全充电的情况下,模拟输入信号电压与模拟输入脚的电压VAIN就不相同。如果模拟输入信号产生变化,它的变化频率(FAIN)的周期至少应该满足10RC原理,即10 × RAIN × (CAIN Cp)。TAIN = 模拟信号的周期 =1/FAIN因为:TAIN ≥ 10 x RAIN x (CAIN CP)因此:FAIN ≤ 1 / [10 x RAIN x (CAIN CP)]假如:RAIN = 25kΩ,CAIN = 7pF,CP = 3pF,则:FAINmax = 1 / [10 x 25x103 x (7 3)x10-12]即信号源的最高频率FAIN(max)= 400kHz。对于上述给出的信号源特性(容抗与阻抗),它的频率不能超过400kHz,否则ADC的转换结果将是不准确的。三、模拟信号源的阻抗估算上面聊了信号源阻抗和AD输入端的电容对ADC的影响,在这个基础上来看下最大允许信号源阻抗的估算。假定最大允许的误差是1/2 LSB。参照上面的图9中的描述,假定此时输入端不存在输入信号充电不充分的情况。

这样得到误差 = VAIN – Vc 【Vc为内部采样电容CADC上的电压】

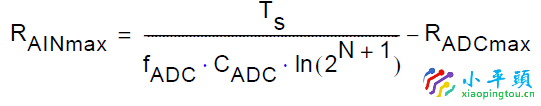

这里tS是采样时间。tS = TS / fADC,其中TS是以ADC时钟周期为单位的采样时钟个数 。对于给定的tS,对应VAIN = VREF 的误差要大于对应VAIN< VREF xss=removed xss=removed>

Rmax = (RAIN RADC)max这里N 是 ADC 分辨率 12我们可以进一步得到:

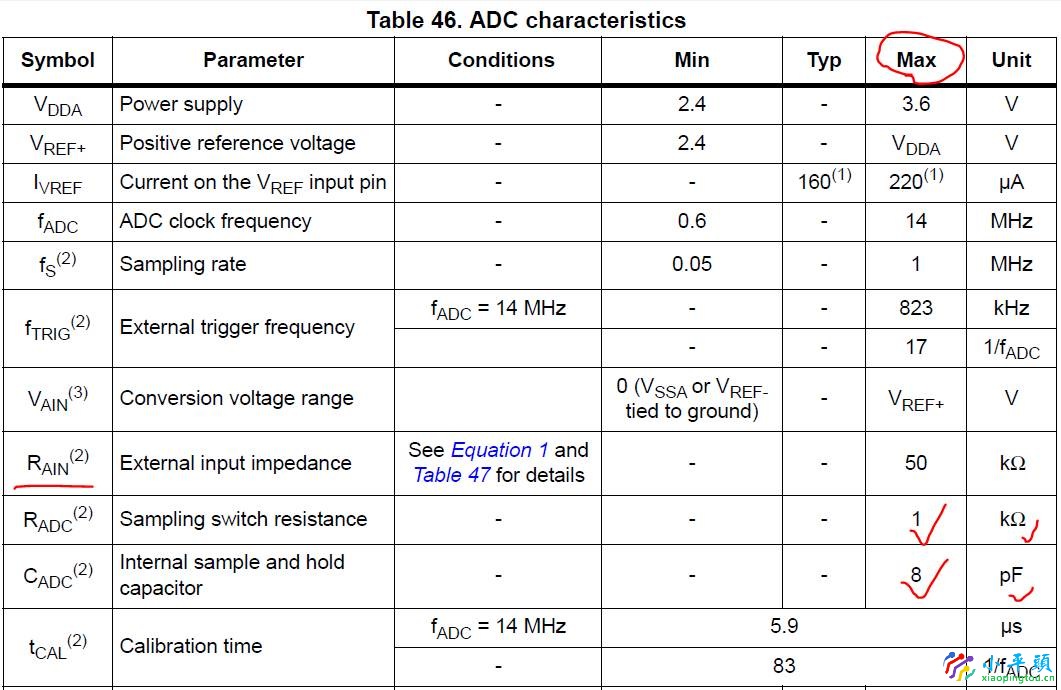

以STM32F103芯片为例,如果这里Ts=7.5, fADC=14MHz,Cadc=12pF,RadcMax=1K,在误差为1/2LSB时的最大允许信号源阻抗为:RAIN(max) = 6.4 k通过上面的分析,我们可以得知选择较长的采样时间或较慢的ADC时钟,能保障更好的转换效果。或者通过降低ADC时钟频率、选择较长采样时间或选择较低的分辨率,可以容许更大的外部信号源阻抗。注:如果使用跟随放大器可以减小信号源的阻抗效应,因为放大器的高输入阻抗和非常低的输出阻抗把RAIN与RADC隔离开来。当然,放大器自身引入的偏移误差也应加以注意和考虑。上面提到的RadcMax、Cadc参数在芯片数据手册的ADC特性表格里,我把STM32F103的截图如下。好,先就聊到这里。整个完整应用笔记请前往官网搜索AN2834,其中有不少关于提高或改善ADC精度的建议,比如关于电源的处理等。

最多设置5个标签!

STM32家族中的所有芯片都内置了逐次逼近寄存器型ADC模块.内部大致框架如下:

每次ADC转换先进行采样保持,然后分多步执行比较输出,步数等于ADC的位数,每个ADC时钟产生一个数据位。说到这里,用过STM32 ADC的人是不是想到了参考手册中关于12位ADC转换时间的公式:

每次ADC转换先进行采样保持,然后分多步执行比较输出,步数等于ADC的位数,每个ADC时钟产生一个数据位。说到这里,用过STM32 ADC的人是不是想到了参考手册中关于12位ADC转换时间的公式:

ST官方就如何保障或改善ADC精度写了一篇应用笔记AN2834。该应用笔记旨在帮助用户了解ADC误差的产生以及如何提高ADC的精度。主要介绍了与ADC设计的相关内容,比如外部硬件设计参数,不同类型的ADC误差来源分析等,并提出了一些如何减小误差的设计上建议。

这里我摘取部分内容,结合个人的理解加以整理与大家分享。更多细节可以去搜索AN2834下载细看。

当我们在做STM32的ADC应用遇到转换结果不如意时,常有人提醒或建议你对采样时间或外部采样电路做调整。这里调整的最终目的就是让信号进入ADC模块的充电时间与内部采样时间匹配,保证采得的电压尽量真实,最终得到符合精度要求的转换结果。下面就聊聊相关话题。

一、模拟信号源阻抗的影响

在做ADC操作时,在信号源与ADC引脚之间,或者说在串行电阻RAIN与ADC引脚AIN之间总有电流流过,自然会产生压降。内部采样电容CADC的充电由阻容网络中的开关和RADC控制。

显然,对CADC有效的充电由【RADC RAIN】控制,充电时间常数是tc = (RADC RAIN) ×CADC。不难理解如果采样时间小于CADC通过RADC RAIN充电的时间,即ts < tc>可以看出,随着电阻(RADC RAIN)的增加,对保持电容的充电时间也需要相应增加。对于STM32而言,RADC是内部的采样开关电阻,阻值相对固定,具体数值在芯片的数据手册里有给出。所以,这里真正可能变动的电阻就是信号源电阻RAIN了,它的变化影响充电常数,进而影响到芯片内部采样时间的选择。

注:tc是电容CADC充电完全的时间,此时Vc = VAIN(最大1/2LSB 误差)

Vc:采样电容CADC上的电压

tc = (RADC RAIN) × CADC 【CADC的值也是相对固定的】

二、信号源的容抗与PCB分布电容的对ADC的影响

做ADC时,除了考虑信号源端的电阻外,还需要考虑信号源本身容抗和在模拟输入端的分布电容(参见下图)。信号源的电阻和电容构成一个阻容网络,如果外部的电容(CAIN Cp)没能完全充电至输入信号电压,ADC转换的结果显然是不准确的。(CAIN Cp)的值越大,信号源的频率也就越受限制。(信号源上的外部电容和分布电容分别用CAIN和Cp表示。)

当外部电路的电容没有被模拟信号源完全充电的情况下,模拟输入信号电压与模拟输入脚的电压VAIN就不相同。如果模拟输入信号产生变化,它的变化频率(FAIN)的周期至少应该满足10RC原理,即10 × RAIN × (CAIN Cp)。

TAIN = 模拟信号的周期 =1/FAIN

因为:TAIN ≥ 10 x RAIN x (CAIN CP)

因此:FAIN ≤ 1 / [10 x RAIN x (CAIN CP)]

假如:RAIN = 25kΩ,CAIN = 7pF,CP = 3pF,则:

FAINmax = 1 / [10 x 25x103 x (7 3)x10-12]

即信号源的最高频率FAIN(max)= 400kHz。

对于上述给出的信号源特性(容抗与阻抗),它的频率不能超过400kHz,否则ADC的转换结果将是不准确的。

三、模拟信号源的阻抗估算

上面聊了信号源阻抗和AD输入端的电容对ADC的影响,在这个基础上来看下最大允许信号源阻抗的估算。假定最大允许的误差是1/2 LSB。

参照上面的图9中的描述,假定此时输入端不存在输入信号充电不充分的情况。

这样得到误差 = VAIN – Vc 【Vc为内部采样电容CADC上的电压】

这里tS是采样时间。

tS = TS / fADC,其中TS是以ADC时钟周期为单位的采样时钟个数 。

对于给定的tS,对应VAIN = VREF 的误差要大于对应VAIN< VREF xss=removed xss=removed>

Rmax = (RAIN RADC)max

这里N 是 ADC 分辨率 12

我们可以进一步得到:

以STM32F103芯片为例,如果这里Ts=7.5, fADC=14MHz,Cadc=12pF,RadcMax=1K,在误差为1/2LSB时的最大允许信号源阻抗为:RAIN(max) = 6.4 k

通过上面的分析,我们可以得知选择较长的采样时间或较慢的ADC时钟,能保障更好的转换效果。或者通过降低ADC时钟频率、选择较长采样时间或选择较低的分辨率,可以容许更大的外部信号源阻抗。

注:如果使用跟随放大器可以减小信号源的阻抗效应,因为放大器的高输入阻抗和非常低的输出阻抗把RAIN与RADC隔离开来。当然,放大器自身引入的偏移误差也应加以注意和考虑。

上面提到的RadcMax、Cadc参数在芯片数据手册的ADC特性表格里,我把STM32F103的截图如下。好,先就聊到这里。整个完整应用笔记请前往官网搜索AN2834,其中有不少关于提高或改善ADC精度的建议,比如关于电源的处理等。

一周热门 更多>