AM3358 gpmc 时钟问题,大侠们帮忙看看 多谢

2019-03-26 15:05发布

打开微信“扫一扫”,打开网页后点击屏幕右上角分享按钮

- GPMC同步方式和FPGA通讯:fpga端发现gpmc_clk 100MHz不稳定;

- RM手册中提到gpmc_clk外接33欧电阻,这个对时钟信号反射有多大影响,如果没有接会有什么问题?

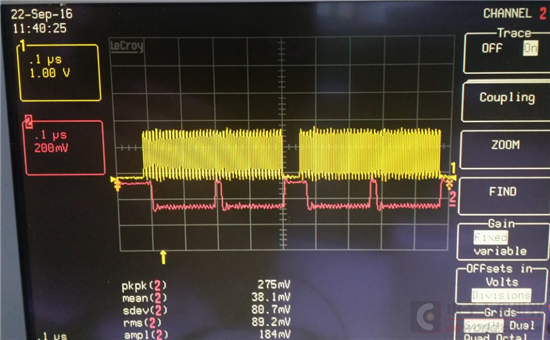

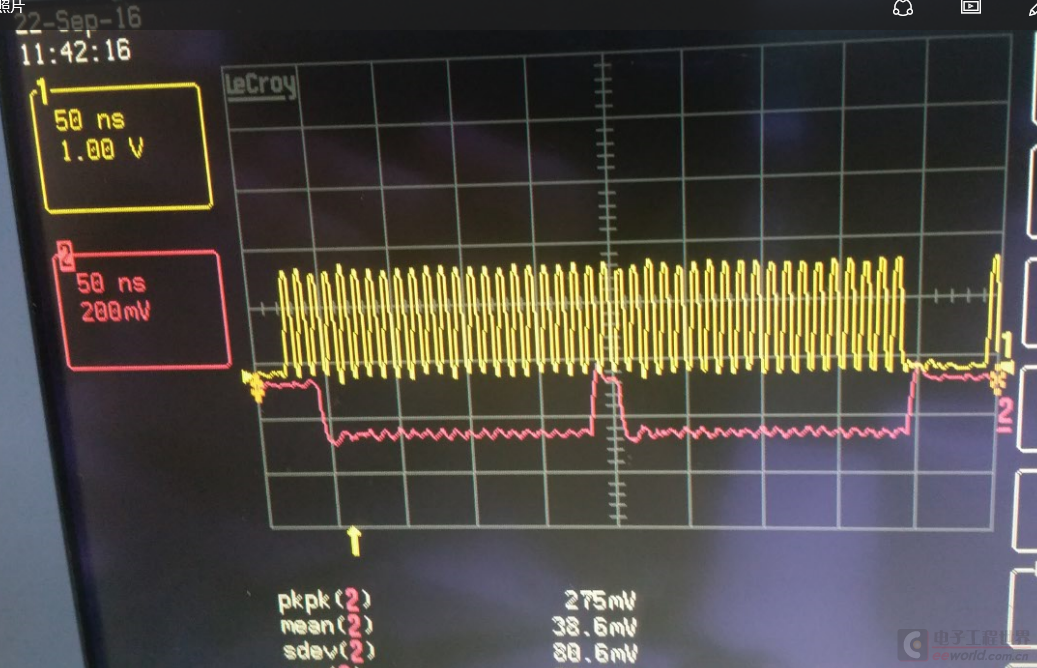

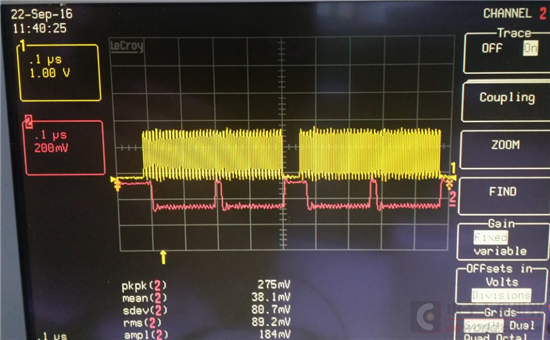

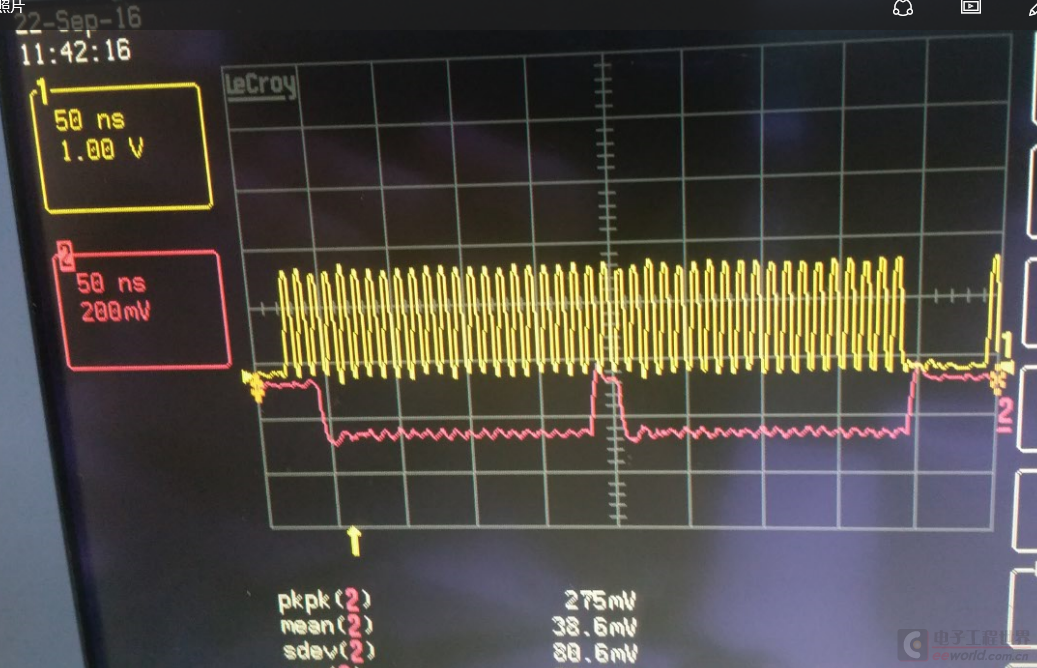

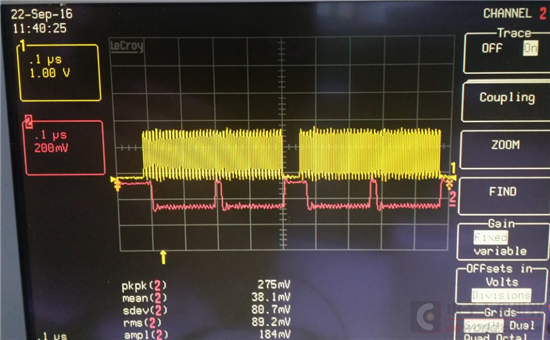

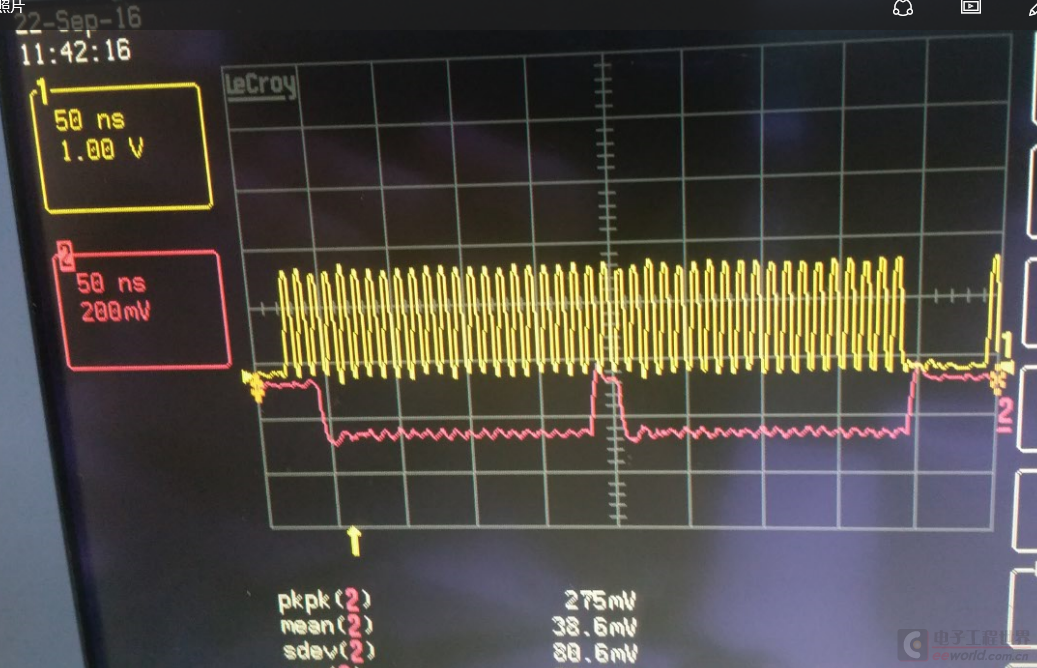

寄存器配置如下: Reg[0x88c] = 0x30;Config配置值如下:GPMC_CONFIG1(FPGA_CS1_CHIP))= (1 << GPMC_CONFIG1_1_DEVICESIZE_SHIFT) | (2 << GPMC_CONFIG1_1_ATTACHEDDEVICEPAGELENGTH_SHIFT) | (1 << GPMC_CONFIG1_1_WRITETYPE_SHIFT) | (1 << GPMC_CONFIG1_1_WRITEMULTIPLE_SHIFT) (1 << GPMC_CONFIG1_1_READTYPE_SHIFT) | (1 << GPMC_CONFIG1_1_READMULTIPLE_SHIFT) | ;GPMC_CONFIG2(FPGA_CS1_CHIP)) = (5 << GPMC_CONFIG2_1_CSRDOFFTIME_SHIFT) | (5 << GPMC_CONFIG2_1_CSWROFFTIME_SHIFT); GPMC_CONFIG3(FPGA_CS1_CHIP)) = (2 << GPMC_CONFIG3_1_ADVRDOFFTIME_SHIFT) | (2 << GPMC_CONFIG3_1_ADVWROFFTIME_SHIFT) | GPMC_CONFIG4(FPGA_CS1_CHIP)) = (2 << GPMC_CONFIG4_1_OEONTIME_SHIFT) | (4 << GPMC_CONFIG4_1_OEOFFTIME_SHIFT) | (2 << GPMC_CONFIG4_1_WEONTIME_SHIFT) | (4 << GPMC_CONFIG4_1_WEOFFTIME_SHIFT); GPMC_CONFIG5(FPGA_CS1_CHIP)) = (6 << GPMC_CONFIG5_1_RDCYCLETIME_SHIFT) | (6 << GPMC_CONFIG5_1_WRCYCLETIME_SHIFT) | (4 << GPMC_CONFIG5_1_RDACCESSTIME_SHIFT) | (1 << GPMC_CONFIG5_1_PAGEBURSTACCESSTIME_SHIFT); GPMC_CONFIG6(FPGA_CS1_CHIP)) = (1 << GPMC_CONFIG6_1_BUSTURNAROUND_SHIFT) | (4 << GPMC_CONFIG6_1_WRACCESSTIME_SHIFT);使用示波器抓取的gpmc_clk和wen信号如图所示: 100MHz CH1是gpmc_clk, CH2是WEn,不知道下面图是否正确? WEn有效时是否应该正好有16个gpmc_clk? 我这里数的有18个gpmc_clk.

此帖出自

小平头技术问答

一周热门 更多>