您好! DSP是TMS320C6678,FPGA是xilinx kintex 7,调试的时候DSP软件使用的是KI_STK_C6670_6678_6614里面的SRIO例子, 程序默认的如下:serdes_cfg.commonSetup.inputRefClock_MHz = 312.5; 和我板子相符合

修改如下: 1、SRIO_Loopback_Mode loopback_mode= SRIO_NO_LOOPBACK; 2、 uiDspNum=1; //跑DSP1程序 3、srio_cfg.srio_1x2x4x_path_control=SRIO_PATH_CTL_1xLaneA 4、srio_cfg.blockEn.bLogic_Port_EN[0]= TRUE;问题:程序会停在 /*---------wait all enabled ports OK-------------*/

for(i=0; i<SRIO_MAX_PORT_NUM; i++)

{

if(srio_cfg->blockEn.bLogic_Port_EN)

{

while(0==(gpSRIO_regs->RIO_SP.RIO_SP_ERR_STAT&

CSL_SRIO_RIO_SP_ERR_STAT_PORT_OK_MASK));

}

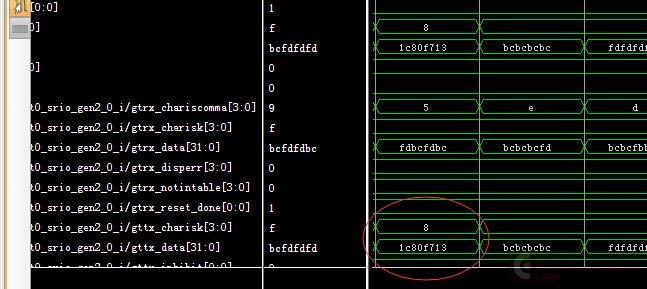

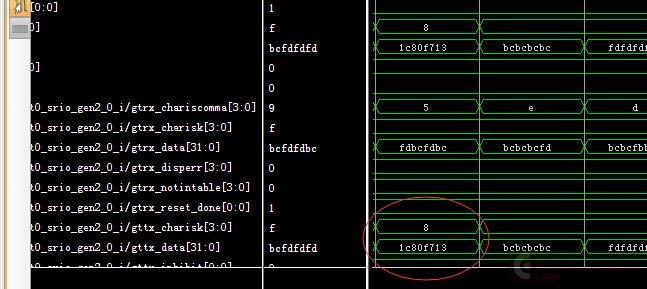

}FPGA这端,我用chipscope抓图发现gttx_data一直在发送control symbol(0x1C80F713),但是gtrx_data却一直没有收到回复的control symbol。图片。

请问是不是DSP还需要设置什么?为什么Port OK一直不拉高?谢谢!

修改如下: 1、SRIO_Loopback_Mode loopback_mode= SRIO_NO_LOOPBACK; 2、 uiDspNum=1; //跑DSP1程序 3、srio_cfg.srio_1x2x4x_path_control=SRIO_PATH_CTL_1xLaneA 4、srio_cfg.blockEn.bLogic_Port_EN[0]= TRUE;问题:程序会停在 /*---------wait all enabled ports OK-------------*/

for(i=0; i<SRIO_MAX_PORT_NUM; i++)

{

if(srio_cfg->blockEn.bLogic_Port_EN)

{

while(0==(gpSRIO_regs->RIO_SP.RIO_SP_ERR_STAT&

CSL_SRIO_RIO_SP_ERR_STAT_PORT_OK_MASK));

}

}FPGA这端,我用chipscope抓图发现gttx_data一直在发送control symbol(0x1C80F713),但是gtrx_data却一直没有收到回复的control symbol。图片。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>