本帖最后由 我的学号 于 2017-8-8 15:12 编辑

大家好,小弟日前在怼自制的28377D 电路板时遇到了无法将晶振的信号倍频的问题,具体的情况是:

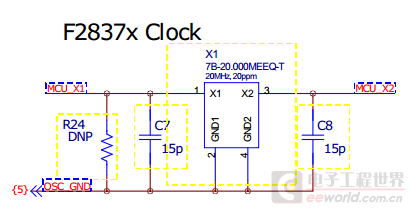

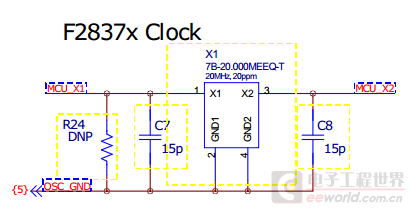

1.电路设计参照 Ti 官方,原理图和布线图如下所示:

2.使用20MHz 的晶振,型号和官方的略不同,但按照晶振数据手册匹配了10pf 的电容,通电时用示波器可见晶振两端正常起振;

3.电路中的复位电路已被切除

4.点灯程序从Ti 的ControlSuit import 进来,在官方的DEMO 板上运行正常;

5.使用仿真器单步调试程序时,运行到设置PLL 函数 InitSysPll (XTAL_OSC,IMULT_20,FMULT_1,PLLCLK_BY_2)里的

// Enable PLLSYSCLK is fed from system PLL clock

ClkCfgRegs.SYSPLLCTL1.bit.PLLCLKEN = 1;

时CCS 提示目标芯片处于 low-power mode,仿真器和芯片的连接断开,同时可见377的复位引脚有低电平输出

6. 调整InitSysPll (XTAL_OSC,IMULT_20,FMULT_1,PLLCLK_BY_2) 的参数,倍频为20MHz,40MHz,60MHz芯片能正常运行,升到80MHz时出现步骤5 无法连接目标芯片的情况

7.检查过MCU 供电的3.3v 和 1.2v 电压都是正常的,布线和引脚使用基本都是参照官方DEMO 板的8.打样回来的同一批的28377电路板也会出现同样情况

至此总觉得距离答案很近,但又不知可以怀疑什么,烦扰两个星期,希望有遇到过相似问题的坛友多多指教,谢谢

此帖出自小平头技术问答

大家好,小弟日前在怼自制的28377D 电路板时遇到了无法将晶振的信号倍频的问题,具体的情况是:

1.电路设计参照 Ti 官方,原理图和布线图如下所示:

2.使用20MHz 的晶振,型号和官方的略不同,但按照晶振数据手册匹配了10pf 的电容,通电时用示波器可见晶振两端正常起振;

3.电路中的复位电路已被切除

4.点灯程序从Ti 的ControlSuit import 进来,在官方的DEMO 板上运行正常;

5.使用仿真器单步调试程序时,运行到设置PLL 函数 InitSysPll (XTAL_OSC,IMULT_20,FMULT_1,PLLCLK_BY_2)里的

// Enable PLLSYSCLK is fed from system PLL clock

ClkCfgRegs.SYSPLLCTL1.bit.PLLCLKEN = 1;

时CCS 提示目标芯片处于 low-power mode,仿真器和芯片的连接断开,同时可见377的复位引脚有低电平输出

6. 调整InitSysPll (XTAL_OSC,IMULT_20,FMULT_1,PLLCLK_BY_2) 的参数,倍频为20MHz,40MHz,60MHz芯片能正常运行,升到80MHz时出现步骤5 无法连接目标芯片的情况

7.检查过MCU 供电的3.3v 和 1.2v 电压都是正常的,布线和引脚使用基本都是参照官方DEMO 板的8.打样回来的同一批的28377电路板也会出现同样情况

至此总觉得距离答案很近,但又不知可以怀疑什么,烦扰两个星期,希望有遇到过相似问题的坛友多多指教,谢谢

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

等我板子做好了,咱们一起学吧。

感谢回复。

但后边选择芯片内部时钟倍频时还是同样升到80MHZ 就会断开 JTAG DEBUG 模式,这点让我十分困惑

把晶振的地和MCU 的地连接起来,这是在无意中解决的

把晶振的地和MCU 的地连接起来,这是在无意中解决的

一周热门 更多>