1.zip

(314.98 KB, 下载次数: 3)

1.zip

(314.98 KB, 下载次数: 3)

附件1.zip是我的所有代码。

===分割线===

这里我描述一下我遇到问题的过程。

我的思路是,现在Quartus里面处理mif文件,生成 .v 文件。

根据 FPGA笔记(九)-实现ROM步骤 文章的内容,编写如下mif文件内容。

Data.mif

- DEPTH=64;

- WIDTH=24;

- ADDRESS_RADIX=HEX;

- DATA_RADIX=HEX;

- CONTENT BEGIN

- 00 : 018108;

- 01 : 00ED82;

- 02 : 00C050;

- 03 : 00E004;

- 04 : 00B005;

- 05 : 01A206;

- 06 : 959A01;

- 07 : 00E00F;

- 08 : 00ED8A;

- 09 : 00ED8C;

- 0A : 00A008;

- 0B : 008001;

- 0C : 062009;

- 0D : 062009;

- 0E : 070A08;

- 0F : 038201;

- 10 : 001001;

- 11 : 00ED83;

- 12 : 00ED87;

- 13 : 00ED99;

- 14 : 00ED9C;

- 15 : 31821D;

- 16 : 31821F;

- 17 : 318221;

- 18 : 318223;

- 19 : 00E01A;

- 1A : 00A01B;

- 1B : 070A01;

- 1C : 00D181;

- 1D : 21881E;

- 1E : 019801;

- 1F : 298820;

- 20 : 019801;

- 21 : 118822;

- 22 : 019801;

- 23 : 198824;

- 24 : 019801;

- 25 : 018110;

- 26 : 000002;

- 27 : 000003;

- 28 : 000004;

- 29 : 000005;

- 2A : 000006;

- 2B : 000007;

- 2C : 000008;

- 2D : 000009;

- 2E : 00000A;

- 2F : 00000B;

- 30 : 00000B;

- 31 : 00000D;

- 32 : 00000E;

- 33 : 00000F;

- 34 : 000010;

- 35 : 000011;

- 36 : 000012;

- 37 : 000013;

- 38 : 000014;

- 39 : 000015;

- 3A : 000016;

- 3B : 000017;

- 3C : 000018;

- 3D : 000019;

- 3E : 00001A;

- 3F : 00001C;

- END;

生成如下文件

Task1.v 是顶层模块。[代码内容见1.zip]

Task1_sim.v 是仿真文件。[代码内容见1.zip]

仿真的思路是,clk 每一个单位时间取一次反,address 每5个单位时间取一次+1.

这样的话,ROM每一地址的数据就会被取出来。

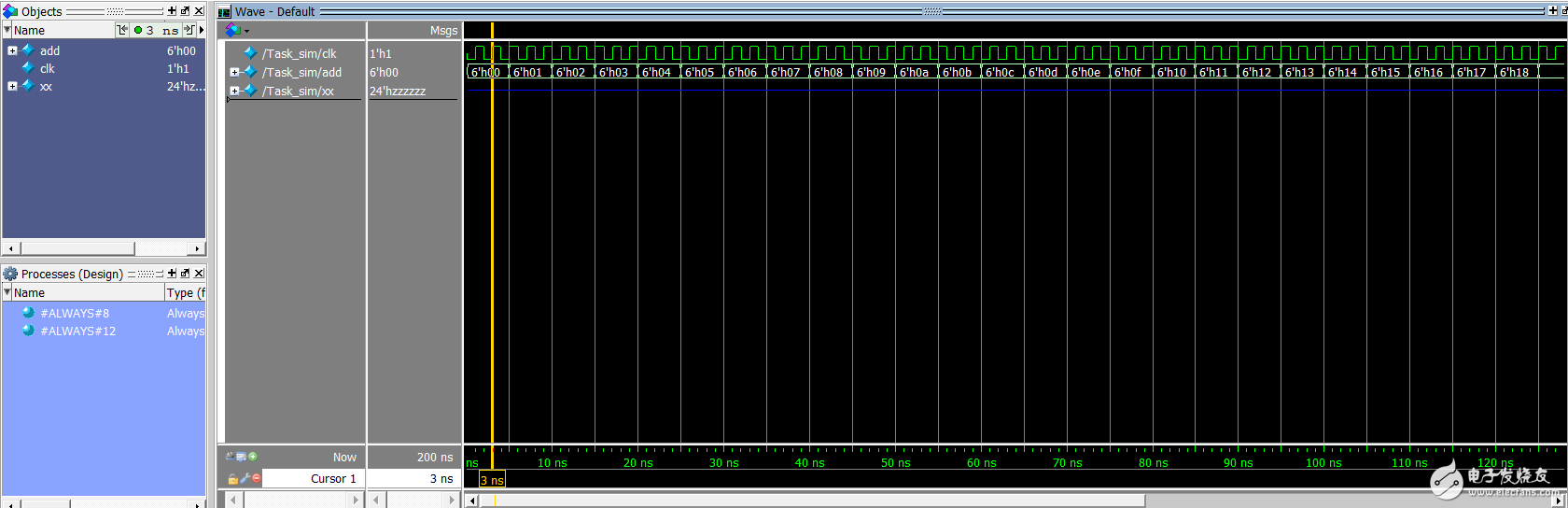

但是最终仿真的结果是这样的

xx 是数据信号,但是一直是高阻态。

然后,根据这篇文章 modelsim仿真fifo和rom时候,输出出现高阻 的内容把 altera_mf.v和220model.v这2个文件加入我的modelsim的工程目录里面进行编译。

效果如下:

但是仿真的结果依旧和之前的一样。

现在我已经没有思路,如何解决这个问题,特来向大家请教。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

modelsim仿真fifo和rom时候,输出出现高阻 https://blog.csdn.net/zd_2010/article/details/41864167

FPGA笔记(九)-实现ROM步骤 https://blog.csdn.net/Struggle_For_M/article/details/51883916

一周热门 更多>