现在需要做1nS脉冲发生器,FPGA可以做出来吗?1,据说FPGA主频达不到1GHz,那通过PLL或MCMM可以吗?如果主频到了,FPGA的普通IO口可以胜任这么高频吗?2,可不可以用FPGA内部GTX(或oserdes)串行收发器编码产生窄脉冲呢,还是这个必须要配合相应的IP核才能用?3,可不可以用锁相环移相的方法,产生较窄脉宽的连续波形,再取其中一个周期输出可不可行?

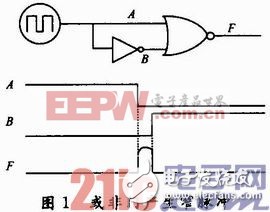

4,还有种说法是利用逻辑器件的竞争冒险方式产生的毛刺,把毛刺当成脉冲,这也是一种方案

大神看看以上这四种方案有哪种可行吗?

4,还有种说法是利用逻辑器件的竞争冒险方式产生的毛刺,把毛刺当成脉冲,这也是一种方案

大神看看以上这四种方案有哪种可行吗?

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

串行500MHz,DDR模式正好可以产生1ns,直接并串转换就行

也有差异。

一周热门 更多>