补充内容 (2017-11-26 22:05):

计数器模块:

module jishuqi(clk_1khz,reset,pause,MSL,MSH,SL,SH,ML,MH);

input clk_1khz,reset,pause;

reg clk_100hz_r;

reg [2:0]cnt_clk;

output reg[3:0]MSL;

output reg[3:0]MSH;

output reg[3:0]SL;

output reg[3:0]SH;

output reg[3:0]ML;

output reg[3:0]MH;

reg cnt_ms;//MSÏòS½øλ

reg cnt_s;//SÏòM½øλ

always@(posedge clk_1khz or negedge reset)

begin

if(!reset)

begin

cnt_clk<=1'b1;

clk_100hz_r<=1'b0;

end

else

begin

if(cnt_clk==3'd5)

begin

cnt_clk<=1'b1;

clk_100hz_r<=~clk_100hz_r;

end

else

cnt_clk<=cnt_clk+1'b1;

end

end

always@(posedge clk_100hz_r or negedge reset)

begin

if(!reset)

begin

MSL<=4'd0;

MSH<=4'd0;

cnt_ms<=1'b0;

end

else

begin

if(!pause)

begin

if(MSL==9)

begin

MSL<=4'd0;

if(MSH==9)

begin

MSH<=4'd0;

cnt_ms<=1'b1;

end

else

begin

MSH<=MSH+1'b1;

cnt_ms<=1'b0;

end

end

else

begin

MSL<=MSL+1'b1;

cnt_ms<=1'b0;

end

end

end

end

always@(posedge cnt_ms or negedge reset)

begin

if(!reset)

begin

SL<=4'd0;

SH<=4'd0;

cnt_s<=1'b0;

end

else

begin

if(!pause)

begin

if(SL==9)

begin

SL<=4'd0;

if(SH==5)

begin

cnt_s<=1'b1;

SH<=4'd0;

end

else

begin

cnt_s<=1'b0;

SH<=SH+1'b1;

end

end

else

begin

SL<=SL+1'b1;

cnt_s<=1'b0;

end

end

end

end

always@(posedge cnt_s or negedge reset)

begin

if(!reset)

begin

ML<=4'd0;

MH<=4'd0;

end

else

begin

if(!pause)

begin

if(ML==9)

begin

ML<=4'd0;

if(MH==5)

begin

MH<=4'd0;

end

else

MH<=MH+1'b1;

end

else

begin

ML<=ML+1'b1;

end

end

end

end

endmodule

...........................................................

数码管扫描模块:

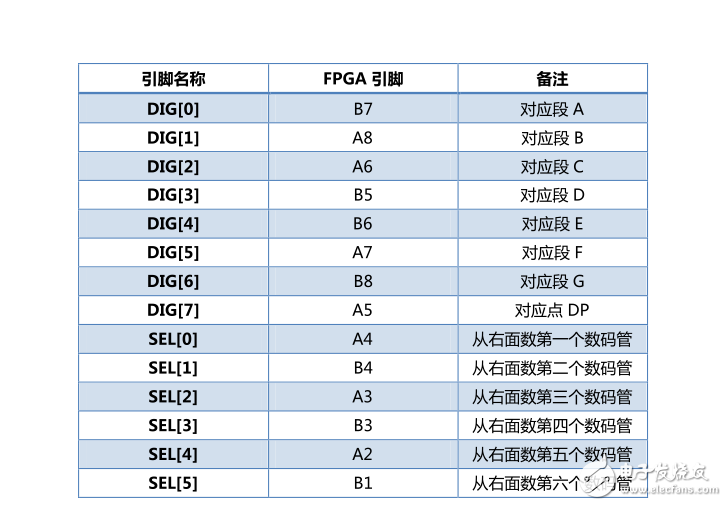

module segscan(clk_1khz,reset,MSL,MSH,SL,SH,ML,MH,sel,data,dp);

input clk_1khz,reset;

input [3:0]MH;

input [3:0]ML;

input [3:0]SL;

input [3:0]SH;

input [3:0]MSL;

input [3:0]MSH;

output reg [3:0]data;//?????????????

output reg [5:0]sel;//????

output reg dp;

reg [2:0]cnt;

always@(posedge clk_1khz or negedge reset)

begin

if(!reset)

cnt<=3'd1;

else

begin

if(cnt==3'd6)

cnt<=3'd1;

else

cnt<=cnt+1'b1;

end

end

always@(posedge clk_1khz or negedge reset)

begin

if(!reset)

sel<=6'b111111;

else

begin

case(cnt)

3'b001:sel<=6'b111110;

3'b010:sel<=6'b111101;

3'b011:sel<=6'b111011;

3'b100:sel<=6'b110111;

3'b101:sel<=6'b101111;

3'b110:sel<=6'b011111;

default:sel<=6'b111111;

endcase

end

end

always@(posedge clk_1khz)

begin

case(sel)

6'b111110:begin dp<=1'b1;end

6'b111101:begin dp<=1'b1;end

6'b111011:begin dp<=1'b0;end

6'b110111:begin dp<=1'b1;end

6'b101111:begin dp<=1'b1;end

6'b011111:begin dp<=1'b1;end

default:begin dp<=1'b1;end

endcase

end

always@(posedge clk_1khz)

begin

if(!reset)

data<=4'b0;

else

begin

case(cnt)

3'b110:begin data<=MH;end

3'b101:begin data<=ML;end

3'b100:begin data<=SH;end

3'b011:begin data<=SL;end

3'b010:begin data<=MSH;end

3'b001:begin data<=MSL;end

default:begin data<=4'd0;end

endcase

end

end

endmodule

.............................................................................

段选模块:

module decode4_7(clk_1khz,reset,data,decout);

input clk_1khz,reset;

input [3:0]data;

output reg [6:0]decout;

always@(negedge clk_1khz or negedge reset)

begin

if(!reset)

decout<=7'b1000000;

else

begin

case(data)

4'd0:decout<=1000000;

4'd1:decout<=1111001;

4'd2:decout<=0100100;

4'd3:decout<=0110000;

4'd4:decout<=0011001;

4'd5:decout<=0010010;

4'd6:decout<=0000010;

4'd7:decout<=1111000;

4'd8:decout<=0000000;

4'd9:decout<=0010000;

default:decout<=7'b1000000;

endcase

end

end

endmodule

............................................................

顶层:

module shuzipaobiao_top (clk_in,rst,sw_onoff,sel,decout,dp);

input clk_in,rst,sw_onoff;

output wire[6:0]decout;//7λ¶ÎÑ¡ÊýÂë¹Ü

output wire[5:0]sel;//λѡ

output wire dp;

wire [3:0]data;

wire [3:0]MSL;wire [3:0]MSH;wire [3:0]SL;wire [3:0]SH;wire [3:0]ML;wire [3:0]MH;

paobiao_fenpin fp(.clk_in(clk_in),.rst(rst),.clk_1khz(clk_1khz));

xiaodou xiao(.clk_1khz(clk_1khz),.rst(rst),.sw_onoff(sw_onoff),.reset(reset),.on_off(on_off));

jishuqi jishu(.clk_1khz(clk_1khz),.reset(reset),.pause(pause),.MSL(MSL),.MSH(MSH),.SL(SL),.SH(SH),.ML(ML),.MH(MH));

control_cnt cntrol(.clk_1khz(clk_1khz),.reset(reset),.on_off(on_off),.pause(pause));

segscan scan_tb(.clk_1khz(clk_1khz),.reset(reset),.MSL(MSL),.MSH(MSH),.SL(SL),.SH(SH),.ML(ML),.MH(MH),.sel(sel),.dp(dp),.data(data));

decode4_7 decode(.clk_1khz(clk_1khz),.reset(reset),.data(data),.decout(decout));

endmodule

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

显示不对,现在已经弄好了。译码不对

一周热门 更多>