本人安装的是Quartus17.0-Lite(配套Modelsim-Altera)

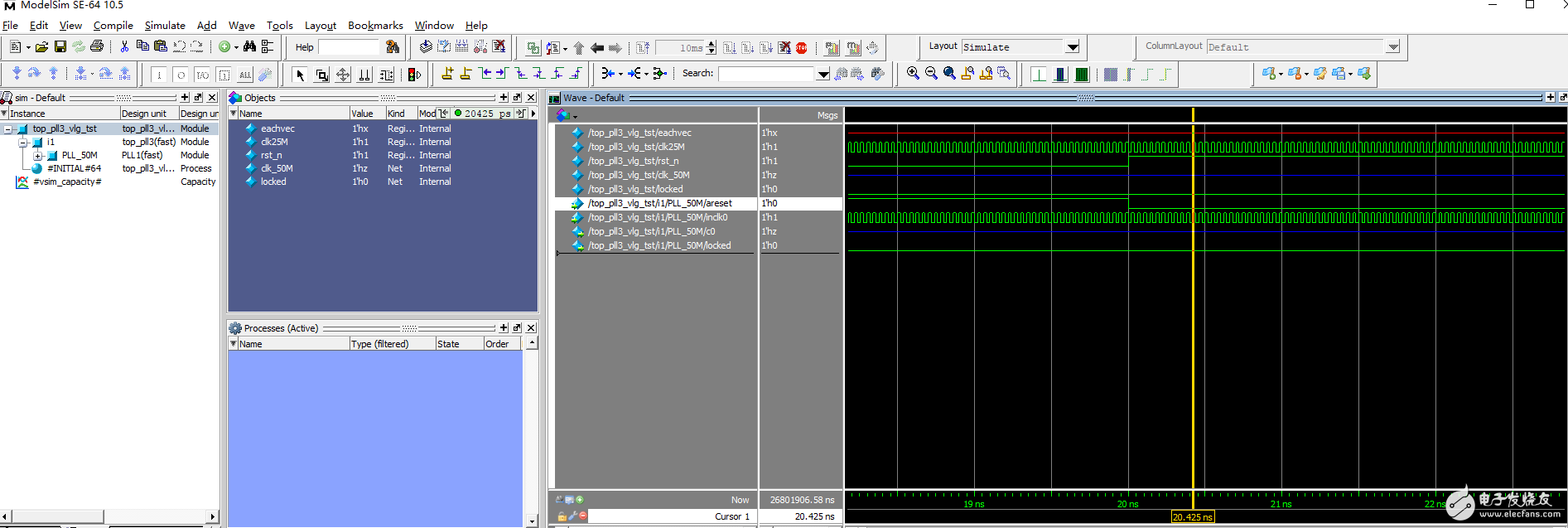

添加PLL的IP核,仿真的时候c0输出高阻,locked一直输出低;

选用:Cyclone10的10CL016E144C8

目前尝试办法:

①选择Cyclone4的器件,调用C4的PLL IP仿真,IP可以正常仿真;

②更换Modelsim SE10.5(破解版),仿真c0输出高阻;

③安装Quartus17.0-stand(破解版),仿真c0输出高阻;

④自己重新编译了ModelSim的Altera库,依然c0输出高阻;

求大神指导指导。

注:目前器件不能变更,最终是要使用Cyclone10LP的,而目前只有Quartus17.0支持Cyclone10LP;

添加PLL的IP核,仿真的时候c0输出高阻,locked一直输出低;

选用:Cyclone10的10CL016E144C8

目前尝试办法:

①选择Cyclone4的器件,调用C4的PLL IP仿真,IP可以正常仿真;

②更换Modelsim SE10.5(破解版),仿真c0输出高阻;

③安装Quartus17.0-stand(破解版),仿真c0输出高阻;

④自己重新编译了ModelSim的Altera库,依然c0输出高阻;

求大神指导指导。

注:目前器件不能变更,最终是要使用Cyclone10LP的,而目前只有Quartus17.0支持Cyclone10LP;

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

①top_pll3:

module top_pll3(

clk25M,

rst_n,

clk_50M,

locked

);

input clk25M;

input rst_n;

output clk_50M;

output locked;

wire clk_50M;

wire locked;

wire clk_c0;

PLL1 PLL_50M(

.areset (~rst_n),

.inclk0 (clk25M),

.c0 (clk_50M),

// .c1 (clk_200M)

.locked (locked)

);

endmodule

②testbench代码:

`timescale 1 ps/ 1 ps

module top_pll3_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg clk25M;

reg rst_n;

// wires

wire clk_50M;

wire locked;

// assign statements (if any)

top_pll3 i1 (

// port map - connection between master ports and signals/registers

.clk25M(clk25M),

.clk_50M(clk_50M),

.locked(locked),

.rst_n(rst_n)

);

initial begin

// Initialize Inputs

rst_n = 1'b1;

#10000;

rst_n = 1'b0;

#10000;

rst_n = 1'b1;

#10000;

/* rst_n = 1'b0;

#1000;

rst_n = 1'b1;

#1000; */

end

//clk initialzation

initial begin

clk25M = 1'b0;

forever

#20 clk25M = ~clk25M;

end

endmodule

目前一个比较折中的解决方案是:器件选10CL16型号,但是PLL选用Cyclone V的PLL库,是能够正常综合编译、仿真的。但这种办法还没有进行上板验证。

另外:过几天出新版17.1,到时候再尝试一下,看看是否可以解决,同时咨询技术支持,看看是否有合理的解释,后面有新结果了再更新,希望不要出现同样的坑。

一周热门 更多>