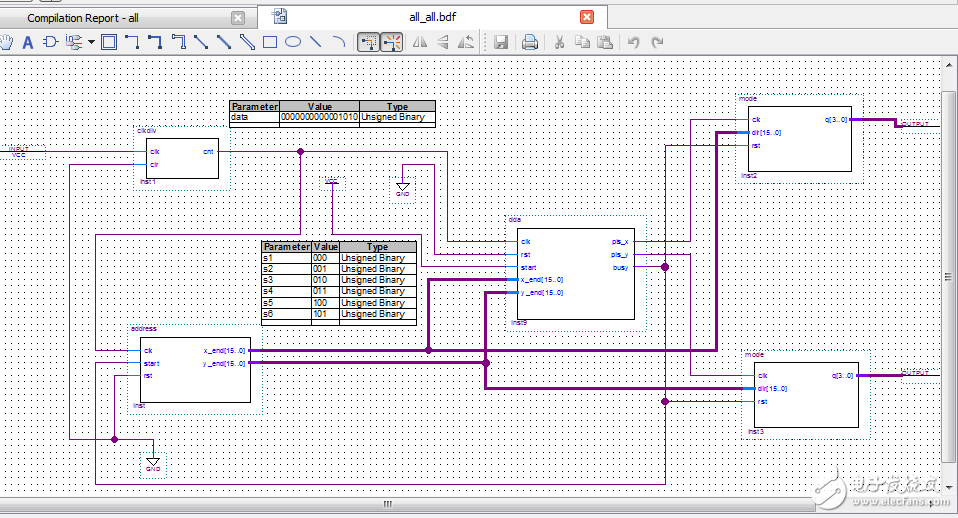

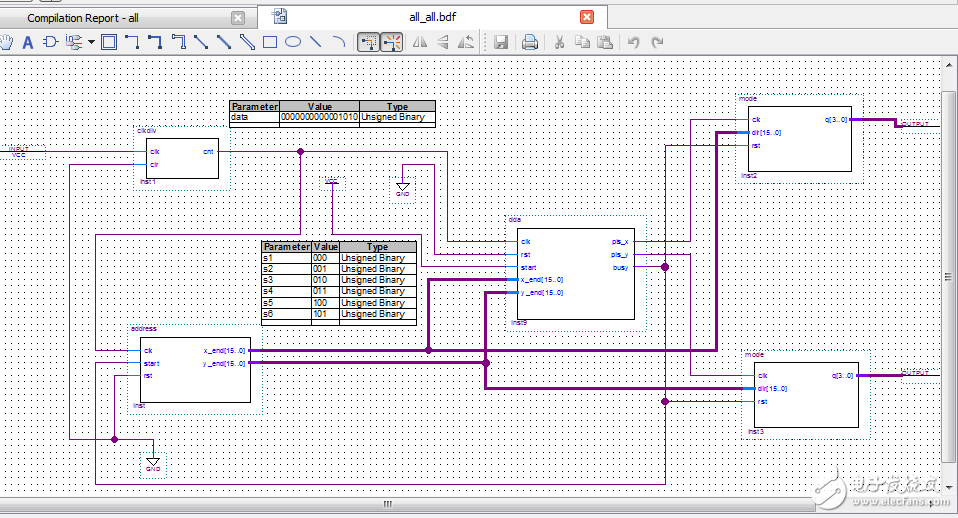

我的这个设计是实现两个坐标轴联动。1、先用verilog语言把分频器模块(clkdiv)、地址发生器模块(address)、积分插补器模块(dda)、工作方式控制器模块(mode)都编写完编译仿真都没有问题。

2、然后生成自原理图,将各自输入输出连接起来以后,存为all_all.bdf文件。

3、将.bdf文件转换为.v文件后编译仿真,此时不出波形。

求大神们告知是什么原因呢?

这是.bdf文件

以下是由.bdf生成的.v文件:

module all(

clk,

q1,

q2

);

input wire clk;

output wire [3:0] q1;

output wire [3:0] q2;

wire SYNTHESIZED_WIRE_15;

wire SYNTHESIZED_WIRE_16;

wire SYNTHESIZED_WIRE_17;

wire SYNTHESIZED_WIRE_4;

wire [15:0] SYNTHESIZED_WIRE_18;

wire SYNTHESIZED_WIRE_7;

wire [15:0] SYNTHESIZED_WIRE_19;

wire SYNTHESIZED_WIRE_11;

wire SYNTHESIZED_WIRE_12;

assign SYNTHESIZED_WIRE_17 = 0;

assign SYNTHESIZED_WIRE_11 = 0;

assign SYNTHESIZED_WIRE_12 = 1;

address b2v_inst(

.clk(SYNTHESIZED_WIRE_15),

.start(SYNTHESIZED_WIRE_16),

.rst(SYNTHESIZED_WIRE_17),

.x_end(SYNTHESIZED_WIRE_18),

.y_end(SYNTHESIZED_WIRE_19));

defparam b2v_inst.s1 = 3'b000;

defparam b2v_inst.s2 = 3'b001;

defparam b2v_inst.s3 = 3'b010;

defparam b2v_inst.s4 = 3'b011;

defparam b2v_inst.s5 = 3'b100;

defparam b2v_inst.s6 = 3'b101;

clkdiv b2v_inst1(

.clk(clk),

.clr(SYNTHESIZED_WIRE_17),

.cnt(SYNTHESIZED_WIRE_15));

defparam b2v_inst1.data = 16'b0000000000001010;

mode b2v_inst2(

.clk(SYNTHESIZED_WIRE_4),

.rst(SYNTHESIZED_WIRE_16),

.dir(SYNTHESIZED_WIRE_18),

.q(q1));

mode b2v_inst3(

.clk(SYNTHESIZED_WIRE_7),

.rst(SYNTHESIZED_WIRE_16),

.dir(SYNTHESIZED_WIRE_19),

.q(q2));

dda b2v_inst9(

.clk(SYNTHESIZED_WIRE_15),

.rst(SYNTHESIZED_WIRE_11),

.start(SYNTHESIZED_WIRE_12),

.x_end(SYNTHESIZED_WIRE_18),

.y_end(SYNTHESIZED_WIRE_19),

.pls_x(SYNTHESIZED_WIRE_4),

.pls_y(SYNTHESIZED_WIRE_7),

.busy(SYNTHESIZED_WIRE_16));

endmodule

2、然后生成自原理图,将各自输入输出连接起来以后,存为all_all.bdf文件。

3、将.bdf文件转换为.v文件后编译仿真,此时不出波形。

求大神们告知是什么原因呢?

以下是由.bdf生成的.v文件:

module all(

clk,

q1,

q2

);

input wire clk;

output wire [3:0] q1;

output wire [3:0] q2;

wire SYNTHESIZED_WIRE_15;

wire SYNTHESIZED_WIRE_16;

wire SYNTHESIZED_WIRE_17;

wire SYNTHESIZED_WIRE_4;

wire [15:0] SYNTHESIZED_WIRE_18;

wire SYNTHESIZED_WIRE_7;

wire [15:0] SYNTHESIZED_WIRE_19;

wire SYNTHESIZED_WIRE_11;

wire SYNTHESIZED_WIRE_12;

assign SYNTHESIZED_WIRE_17 = 0;

assign SYNTHESIZED_WIRE_11 = 0;

assign SYNTHESIZED_WIRE_12 = 1;

address b2v_inst(

.clk(SYNTHESIZED_WIRE_15),

.start(SYNTHESIZED_WIRE_16),

.rst(SYNTHESIZED_WIRE_17),

.x_end(SYNTHESIZED_WIRE_18),

.y_end(SYNTHESIZED_WIRE_19));

defparam b2v_inst.s1 = 3'b000;

defparam b2v_inst.s2 = 3'b001;

defparam b2v_inst.s3 = 3'b010;

defparam b2v_inst.s4 = 3'b011;

defparam b2v_inst.s5 = 3'b100;

defparam b2v_inst.s6 = 3'b101;

clkdiv b2v_inst1(

.clk(clk),

.clr(SYNTHESIZED_WIRE_17),

.cnt(SYNTHESIZED_WIRE_15));

defparam b2v_inst1.data = 16'b0000000000001010;

mode b2v_inst2(

.clk(SYNTHESIZED_WIRE_4),

.rst(SYNTHESIZED_WIRE_16),

.dir(SYNTHESIZED_WIRE_18),

.q(q1));

mode b2v_inst3(

.clk(SYNTHESIZED_WIRE_7),

.rst(SYNTHESIZED_WIRE_16),

.dir(SYNTHESIZED_WIRE_19),

.q(q2));

dda b2v_inst9(

.clk(SYNTHESIZED_WIRE_15),

.rst(SYNTHESIZED_WIRE_11),

.start(SYNTHESIZED_WIRE_12),

.x_end(SYNTHESIZED_WIRE_18),

.y_end(SYNTHESIZED_WIRE_19),

.pls_x(SYNTHESIZED_WIRE_4),

.pls_y(SYNTHESIZED_WIRE_7),

.busy(SYNTHESIZED_WIRE_16));

endmodule

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

感觉连原理图比用verilog例化快~我是新手,先.bdf再生成.v这方法也是网上查的,感觉应该也行得通,但不知道为什么就没波形;复位信号一直拉低是为了方便,我这个实现的功能很简单,不用频繁复位所以就这么整了

modelsim不认.bdf,必须生成.v才行。

那还真不知道你那是怎么仿真的,我一般做的时候都是顶层原理图,然后生成激励文件,

1. 复位信号

2. reg型变量的初始化

3. 时钟信号

挨个检查一下就能找出答案了

一周热门 更多>