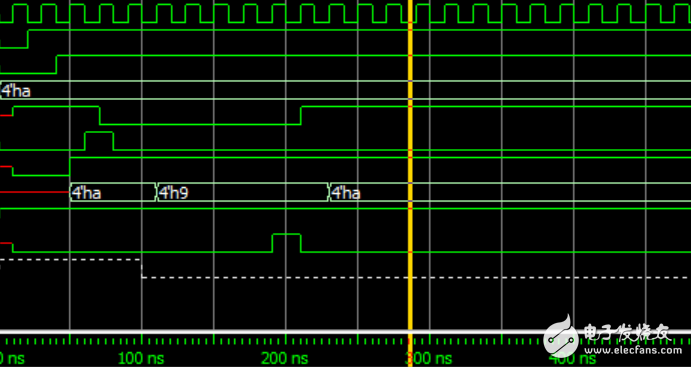

以下程序是关于有效数据之后插入冗余数据,输入输出均遵循AXI-strem协议,我一共插入了7个数据,为啥仿真的时候,插入的冗余数据就显示一个,不该是显示7个相同的数据吗?求各位大侠指点下,谢啦

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2017/04/26 16:33:58

// Design Name:

// Module Name: dummy_insert

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

//端口声明

module dummy_insert(

clk,

rstn,

s_data_tvalid,

s_data_tdata,

s_data_tready,

s_data_tlast,

m_data_tvalid,

m_data_tdata,

m_data_tready,

m_data_tlast

);

parameter INSERT_NUM = 7;

parameter DUMMY_DATA = 4'b1001;

//input and output

input clk;

input rstn;

input s_data_tvalid;

input[3:0] s_data_tdata;

output s_data_tready;

input s_data_tlast;

output m_data_tvalid;

output[3:0] m_data_tdata;

input m_data_tready;

output m_data_tlast;

//插入冗余数据选择标志信号

reg dummy_sel;

always @(posedge clk)

begin

if(rstn == 1'b0) begin

dummy_sel <= 1'b0;

end

else if(s_data_tlast) begin

dummy_sel <= 1'b1;

end

else if(m_data_tlast) begin

dummy_sel <= 1'b0;

end

end

//m_data_tvalid(整个传输时间)

reg m_data_tvalid_t;

reg m_data_tvalid_insert;

wire m_data_tvalid;

//有效数据传输

always @(posedge clk)

begin

if(rstn == 1'b0) begin

m_data_tvalid_t <= 1'b0;

end

else begin

m_data_tvalid_t <= s_data_tvalid;

end

end

//冗余数据传输

always @(posedge clk)

begin

if(rstn == 1'b0) begin

m_data_tvalid_insert <= 1'b0;

end

else begin

m_data_tvalid_insert <= dummy_sel & m_data_tready & s_data_tvalid;

end

end

assign m_data_tvalid = m_data_tvalid_t | m_data_tvalid_insert;

//m_data_tlast

reg [2:0] cnt_dummy;

always @(posedge clk)

begin

if(rstn==1'b0 || s_data_tlast == 1'b1) begin

cnt_dummy <= 2'd0;

end

else if(cnt_dummy < INSERT_NUM && dummy_sel && m_data_tready ) begin

cnt_dummy <= cnt_dummy + 1'b1;

end

end

assign m_data_tlast = (cnt_dummy == INSERT_NUM-1) & m_data_tready;

//m_data_tdata

reg [3:0] m_data_tdata_t;

always @(posedge clk)

begin

if(s_data_tvalid & s_data_tready) begin//有效数据传输

m_data_tdata_t <= s_data_tdata;

end

else if(m_data_tvalid_insert) begin

m_data_tdata_t <= DUMMY_DATA;//冗余数据传输

end

end

assign m_data_tdata = m_data_tdata_t;

//s_data_tready

assign s_data_tready = (~dummy_sel) & m_data_tready;//传有效数据时 为高电平

endmodule

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2017/04/26 16:33:58

// Design Name:

// Module Name: dummy_insert

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

//端口声明

module dummy_insert(

clk,

rstn,

s_data_tvalid,

s_data_tdata,

s_data_tready,

s_data_tlast,

m_data_tvalid,

m_data_tdata,

m_data_tready,

m_data_tlast

);

parameter INSERT_NUM = 7;

parameter DUMMY_DATA = 4'b1001;

//input and output

input clk;

input rstn;

input s_data_tvalid;

input[3:0] s_data_tdata;

output s_data_tready;

input s_data_tlast;

output m_data_tvalid;

output[3:0] m_data_tdata;

input m_data_tready;

output m_data_tlast;

//插入冗余数据选择标志信号

reg dummy_sel;

always @(posedge clk)

begin

if(rstn == 1'b0) begin

dummy_sel <= 1'b0;

end

else if(s_data_tlast) begin

dummy_sel <= 1'b1;

end

else if(m_data_tlast) begin

dummy_sel <= 1'b0;

end

end

//m_data_tvalid(整个传输时间)

reg m_data_tvalid_t;

reg m_data_tvalid_insert;

wire m_data_tvalid;

//有效数据传输

always @(posedge clk)

begin

if(rstn == 1'b0) begin

m_data_tvalid_t <= 1'b0;

end

else begin

m_data_tvalid_t <= s_data_tvalid;

end

end

//冗余数据传输

always @(posedge clk)

begin

if(rstn == 1'b0) begin

m_data_tvalid_insert <= 1'b0;

end

else begin

m_data_tvalid_insert <= dummy_sel & m_data_tready & s_data_tvalid;

end

end

assign m_data_tvalid = m_data_tvalid_t | m_data_tvalid_insert;

//m_data_tlast

reg [2:0] cnt_dummy;

always @(posedge clk)

begin

if(rstn==1'b0 || s_data_tlast == 1'b1) begin

cnt_dummy <= 2'd0;

end

else if(cnt_dummy < INSERT_NUM && dummy_sel && m_data_tready ) begin

cnt_dummy <= cnt_dummy + 1'b1;

end

end

assign m_data_tlast = (cnt_dummy == INSERT_NUM-1) & m_data_tready;

//m_data_tdata

reg [3:0] m_data_tdata_t;

always @(posedge clk)

begin

if(s_data_tvalid & s_data_tready) begin//有效数据传输

m_data_tdata_t <= s_data_tdata;

end

else if(m_data_tvalid_insert) begin

m_data_tdata_t <= DUMMY_DATA;//冗余数据传输

end

end

assign m_data_tdata = m_data_tdata_t;

//s_data_tready

assign s_data_tready = (~dummy_sel) & m_data_tready;//传有效数据时 为高电平

endmodule

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

对呀 ,程序我看着没问题呀 ,但是仿真结果跟我预想的有区别呀,虽然插入了冗余数据,但是我想插7个,它只显示了一个,求大侠解答

一周热门 更多>