图二

图三

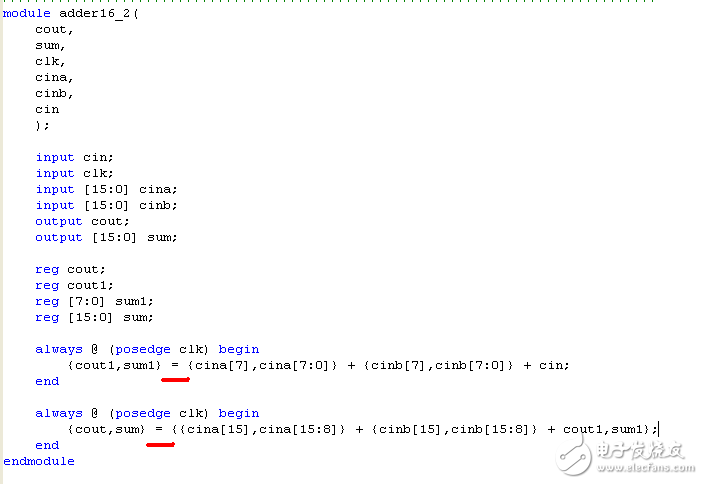

图四

最近写了一个16位二级流水线加法器,并进行了一下仿真。发现在always块中采用阻塞赋值(=)和非阻塞赋值(<=)的结果是不一样的,书上的例程以及网上很多例程的流水线加法器都采用的是阻塞赋值。

书上对流水线加法器的描述是这样的:“采用流水线,能将一个算术操作分解为一些小规模的基本操作,将进位和中间值存储在寄存器中,并在下一个时钟周期内继续运算”。

如上图所示,图一、图二是采用非阻塞赋值的代码及仿真波形图,图三、图四是采用阻塞赋值的代码及波形图。明显可以看出,采用阻塞赋值的仿真结果是在一个时钟周期内得到结果,并没有像描述的那样在每个时钟周期内分级运算,也没有体现出流水线的特点;而非阻塞赋值好像更符合“下一个时钟周期内继续运算”的描述,也体现出了流水线的执行特点。

求大神指点!

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

你了解流水线加法器吗?书上用的是阻塞赋值,但是仿真结果却跟我想象的不一样。我感觉非阻塞赋值的仿真结果更符合流水线执行的特点。是否是我对流水线的理解有偏差?

我要是说这里用阻塞赋值是错误的,会不会有人喷死我

讲讲你的依据吧,我也感觉这里用阻塞赋值有问题,但是没有足够理论支撑

最后为什么不直接用

always@(posedge clk) begin

{cout,sum}<=cina+cinb;

end

不知道你把它分解成,高8Bit和低8bit分别相加是想干什么 ?

一周热门 更多>