本帖最后由 Geekerwwy 于 2016-4-25 14:39 编辑

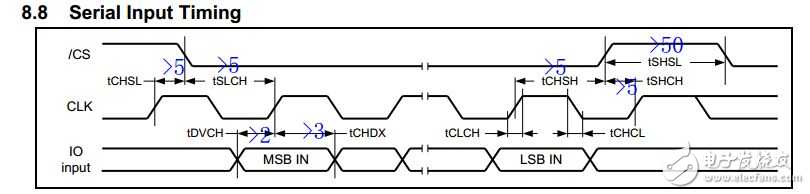

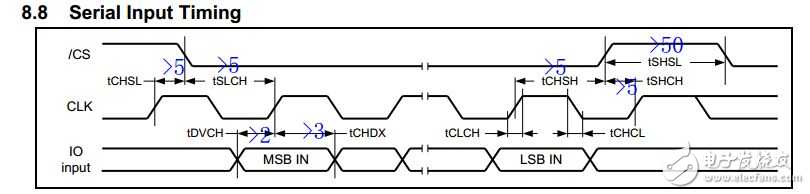

在编写SPI FLASH控制器时遇到了点问题,如下图所示。

举例来说,CS#的下降沿和CLK的上升沿之间需要有tSLCH=5ns的延迟,目前使用的CLK是50MHz,最快不能超过100MHz,也就是说不能通过计数器实现延迟,而且#5这样的语句是不可综合的,这个问题该怎么解决?

希望大神们不吝赐教,小弟先谢过了。

在编写SPI FLASH控制器时遇到了点问题,如下图所示。

举例来说,CS#的下降沿和CLK的上升沿之间需要有tSLCH=5ns的延迟,目前使用的CLK是50MHz,最快不能超过100MHz,也就是说不能通过计数器实现延迟,而且#5这样的语句是不可综合的,这个问题该怎么解决?

希望大神们不吝赐教,小弟先谢过了。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

是这样,但也不会差太多,而且如果用计数器计时,CLK上升沿加一次,这样最小时长也是一个CLK周期,难道要用两个时钟吗?或者用上下降沿?但一般下降沿是不建议使用的。

您是指在CLK的下降沿将CS拉低吗?

nios 生成一个spi接口,里面有源码,自己看!

一周热门 更多>