首先我想实现的是特权同学视频教程中的基于FIFO的串口发送机设计,我用的是Spartan 3E Kit板子,发现综合后少了FIFO例化模块,不知道为什么会出现这种现象,求各位大神指点迷津!

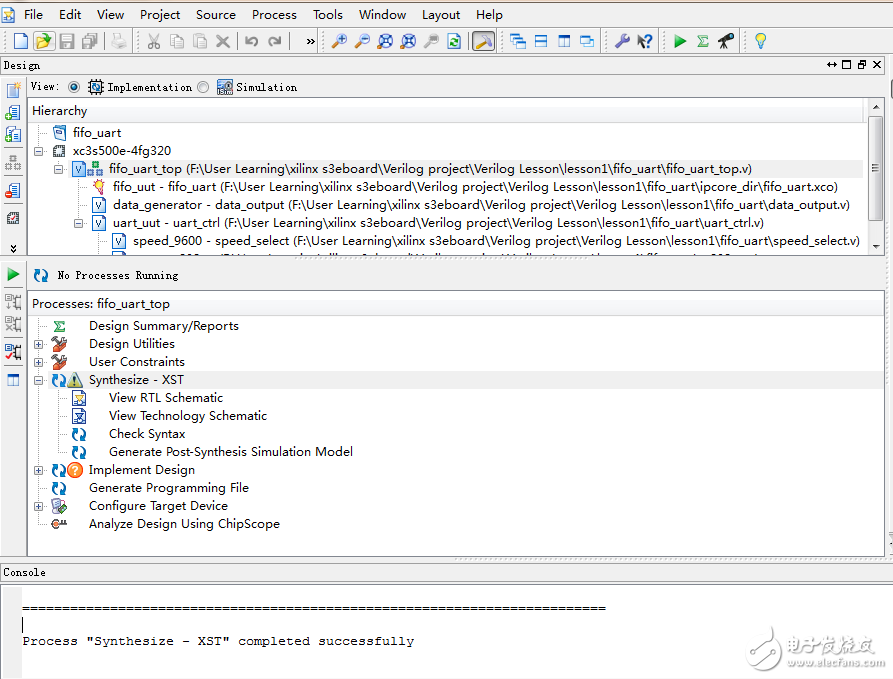

综合后的视图如下:

工程文件结构如下图:

顶层设计代码如下:主要是模块的例化,包括fifo的例化

module fifo_uart_top(clk,rst_n,

rs232_tx

);

input clk,rst_n;

output rs232_tx;

wire [7:0]wr_data_in;

wire [7:0]tx_data;

wire wr_req,rd_req;

wire tx_start;

//例化fifo IP核

fifo_uart fifo_uut(

.clk(clk), // input clk

.rst(rst_n), // input rst

.din(wr_data_in), // input [7 : 0] din

.wr_en(wr_req), // input wr_en

.rd_en(rd_req), // input rd_en

.dout(tx_data), // output [7 : 0] dout

.full(full), // output full

.empty(tx_start) // output empty

);

//例化数据产生模块

data_output data_generator(

.clk(clk),

.rst_n(rst_n),

.wr_req(wr_req),

.wr_data_in(wr_data_in)

);

//例化uart_ctrl模块

uart_ctrl uart_uut(

.clk(clk),

.rst_n(rst_n),

.tx_start(tx_start),

.rs232_tx(rs232_tx),

.tx_data(tx_data),

.rd_req(rd_req)

);

endmodule

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

正确的RTL视图如下:

一周热门 更多>