module getValue1(input clk,

input [7:0]datinB,

input ntrig,

input rdclk,

input [2:0] type1,

input type_en,

input req,

output reg [7:0] datout,

output reg [11:0]rdaddr,

output reg busy,

output reg RDY=0,

output reg [11:0] wraddr

);

reg [2:0] TYPE=4;

reg ntrig_next,busy_next,req_next,startWr; //用于判断边沿,start标识边沿后持续时间段(标识一帧)

reg [2:0] startRd;

reg [7:0] datinB_next; //datinA_next,用于判断过零点

reg [15:0] zeroB[50:0]; //起/始像素点(过零点 pixel)

reg [7:0] averB[25:0];//

reg [7:0] memB[4095:0];

reg [7:0]index_Bz,index_Bs ;//过零点 pixel 数组下标

reg [7:0] index_Bv;//过零点 pixel 数组下标

reg [15:0]index_Bm;//非零像素数组下标

reg startBz;//非零区段标识

reg [7:0] widthB;//

reg [31:0] sumB;//sumA,

reg [15:0]len_memB,len_Rd,len_zeroB;//

reg [7:0] len_averB;//

always @(posedge clk)

begin

//下降沿触发延时,延时一帧处理

ntrig_next<=ntrig;

if((ntrig_next)&(~ntrig)) //下降沿

begin

startWr<=1;

wraddr<=0;

index_Bz<=0;

index_Bv<=0;

index_Bm<=0;///长度可能大于255

end

if(startWr==1)//标识持续读取一帧

begin

busy<=1;

datinB_next<=datinB;

////----B 通道--------

if((datinB_next==0)&&(datinB>0)) //起始点

begin

startBz<=1;

index_Bs<=index_Bz;

zeroB[index_Bz]<=wraddr;//zeroA[1]开始存数据,[0]用于存长度

index_Bz<=index_Bz+1;

sumB<=datinB;//sumB<=0;

end

if(startBz) sumB<=sumB+datinB;

if((datinB_next>0)&&(datinB==0))//终了点

begin

startBz<=0;

zeroB[index_Bz]<=wraddr;

widthB<=wraddr-zeroB[index_Bs];//widthB<=zeroB[index_Bz]-zeroB[index_Bs];

if(((wraddr-zeroB[index_Bs])>0)&&((wraddr-zeroB[index_Bs])<3640))//if((widthB>2)&&(widthB<500)) if((widthB>0)&&(widthB<500))

begin

index_Bz<=index_Bz+1;

averB[index_Bv]=sumB/(wraddr-zeroB[index_Bs]);//averB[index_Bv]=sumB/widthB;

index_Bv<=index_Bv+1;

end

else index_Bz<=index_Bs;//超出,则覆盖本次

end

//---------------------------------------

//------------去掉 0 数值的帧内容---------

if(datinB>0)

begin

memB[index_Bm]=datinB;//自memA[2]开始存数据,[0:1]用于存长度

index_Bm<=index_Bm+1;

end

//-------------------------------

wraddr<=wraddr+1;

end//end startWr==1

if((startWr==1)&&(wraddr>=3647))

begin

startWr<=0;

busy<=0;

//-------B--------

len_zeroB<=(index_Bz<<1);//过零点位置数组 B ,位置16bit,长度*2

// zeroB[0]<=len_zeroB+1;

len_averB<=index_Bv; //平均值数组B

// averB[0]<=len_averB+1;

len_memB<=index_Bm; //非零值数组B

// memB[0]<=len_memB+1;

//---------------

end

//---------------------------------------

end

always @(posedge rdclk)

begin

busy_next<=busy;

req_next<=req;

datout<=8'h0;

if((busy_next==1)&&(busy==0))//(||((~req_next)&(req))) //busy 下降沿 or req 上升沿

begin

startRd<=1;//下降沿触发

RDY<=1;

rdaddr<=0;

case (type1)

3'h4://读取过零点位置数组 B

//len_Rd<=len_zeroB;

begin

len_Rd<=len_zeroB;

if(len_zeroB!=0)

datout<=8'h55;

else

datout<=8'h00;

end

3'h5://读取平均值数组B

//len_Rd<=len_averB;

begin

len_Rd<=len_averB;

if(len_averB!=0)

datout<=8'h55;

else

datout<=8'h00;

end

3'h6://读取 非零数组B

//len_Rd<=len_memB;

begin

len_Rd<=len_memB;

if(len_memB!=0)

datout<=8'h55;

else

datout<=8'h00;

end

default://reserve

datout<=0;

endcase

//datout<=8'h55;

end

if(startRd==1&&len_Rd>0)//

begin

datout<=len_Rd+2; //55 len data

startRd<=2;//startRd<=2;

RDY<=1;

end

if(RDY==1&&len_Rd==0)//清零,防止触发后没有合适的数据,导致RDY一直为1,不停发送零

RDY<=0;

if(startRd==2)//if(startRd==2)

begin

case (type1)

3'h4://读取过零点位置数组 B

begin

if(rdaddr[0]==0) datout<=zeroB[rdaddr>>1][15:8];

if(rdaddr[0]==1) datout<=zeroB[rdaddr>>1][7:0];

end

3'h5://读取平均值数组B

datout<=averB[rdaddr];

3'h6://读取 非零数组B

datout<=memB[rdaddr];

default://reserve

datout<=0;

endcase

rdaddr<=rdaddr+1;

RDY<=1;

end

if((rdaddr>=len_Rd)&&(rdaddr!=0))//if(rdaddr>=len_Rd)//

begin

startRd<=0;

RDY<=0;

rdaddr<=0;

len_Rd<=0;

end

end

endmodule

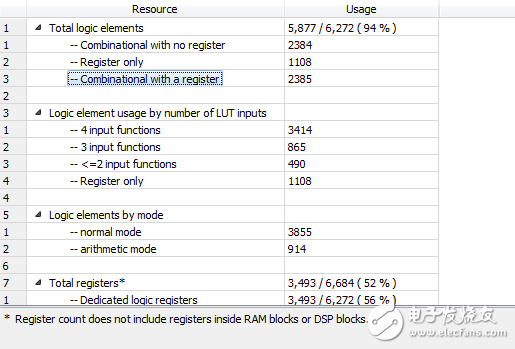

主要占用资源的是以上模块,加上后Total Logic Elements由10%直接增加到94%,芯片型号是cyclone 4 E系列。

图中,如果不把typeA[2..0]连接到getvalue1,Total Logic Elements只用了10%,连接上后,Total Logic Elements直接飙到了94%,请问是哪里出了问题,还是getvalue1模块的问题,getvalue1中的代码有什么优化的方法可以减少Total Logic Elements的使用。

input [7:0]datinB,

input ntrig,

input rdclk,

input [2:0] type1,

input type_en,

input req,

output reg [7:0] datout,

output reg [11:0]rdaddr,

output reg busy,

output reg RDY=0,

output reg [11:0] wraddr

);

reg [2:0] TYPE=4;

reg ntrig_next,busy_next,req_next,startWr; //用于判断边沿,start标识边沿后持续时间段(标识一帧)

reg [2:0] startRd;

reg [7:0] datinB_next; //datinA_next,用于判断过零点

reg [15:0] zeroB[50:0]; //起/始像素点(过零点 pixel)

reg [7:0] averB[25:0];//

reg [7:0] memB[4095:0];

reg [7:0]index_Bz,index_Bs ;//过零点 pixel 数组下标

reg [7:0] index_Bv;//过零点 pixel 数组下标

reg [15:0]index_Bm;//非零像素数组下标

reg startBz;//非零区段标识

reg [7:0] widthB;//

reg [31:0] sumB;//sumA,

reg [15:0]len_memB,len_Rd,len_zeroB;//

reg [7:0] len_averB;//

always @(posedge clk)

begin

//下降沿触发延时,延时一帧处理

ntrig_next<=ntrig;

if((ntrig_next)&(~ntrig)) //下降沿

begin

startWr<=1;

wraddr<=0;

index_Bz<=0;

index_Bv<=0;

index_Bm<=0;///长度可能大于255

end

if(startWr==1)//标识持续读取一帧

begin

busy<=1;

datinB_next<=datinB;

////----B 通道--------

if((datinB_next==0)&&(datinB>0)) //起始点

begin

startBz<=1;

index_Bs<=index_Bz;

zeroB[index_Bz]<=wraddr;//zeroA[1]开始存数据,[0]用于存长度

index_Bz<=index_Bz+1;

sumB<=datinB;//sumB<=0;

end

if(startBz) sumB<=sumB+datinB;

if((datinB_next>0)&&(datinB==0))//终了点

begin

startBz<=0;

zeroB[index_Bz]<=wraddr;

widthB<=wraddr-zeroB[index_Bs];//widthB<=zeroB[index_Bz]-zeroB[index_Bs];

if(((wraddr-zeroB[index_Bs])>0)&&((wraddr-zeroB[index_Bs])<3640))//if((widthB>2)&&(widthB<500)) if((widthB>0)&&(widthB<500))

begin

index_Bz<=index_Bz+1;

averB[index_Bv]=sumB/(wraddr-zeroB[index_Bs]);//averB[index_Bv]=sumB/widthB;

index_Bv<=index_Bv+1;

end

else index_Bz<=index_Bs;//超出,则覆盖本次

end

//---------------------------------------

//------------去掉 0 数值的帧内容---------

if(datinB>0)

begin

memB[index_Bm]=datinB;//自memA[2]开始存数据,[0:1]用于存长度

index_Bm<=index_Bm+1;

end

//-------------------------------

wraddr<=wraddr+1;

end//end startWr==1

if((startWr==1)&&(wraddr>=3647))

begin

startWr<=0;

busy<=0;

//-------B--------

len_zeroB<=(index_Bz<<1);//过零点位置数组 B ,位置16bit,长度*2

// zeroB[0]<=len_zeroB+1;

len_averB<=index_Bv; //平均值数组B

// averB[0]<=len_averB+1;

len_memB<=index_Bm; //非零值数组B

// memB[0]<=len_memB+1;

//---------------

end

//---------------------------------------

end

always @(posedge rdclk)

begin

busy_next<=busy;

req_next<=req;

datout<=8'h0;

if((busy_next==1)&&(busy==0))//(||((~req_next)&(req))) //busy 下降沿 or req 上升沿

begin

startRd<=1;//下降沿触发

RDY<=1;

rdaddr<=0;

case (type1)

3'h4://读取过零点位置数组 B

//len_Rd<=len_zeroB;

begin

len_Rd<=len_zeroB;

if(len_zeroB!=0)

datout<=8'h55;

else

datout<=8'h00;

end

3'h5://读取平均值数组B

//len_Rd<=len_averB;

begin

len_Rd<=len_averB;

if(len_averB!=0)

datout<=8'h55;

else

datout<=8'h00;

end

3'h6://读取 非零数组B

//len_Rd<=len_memB;

begin

len_Rd<=len_memB;

if(len_memB!=0)

datout<=8'h55;

else

datout<=8'h00;

end

default://reserve

datout<=0;

endcase

//datout<=8'h55;

end

if(startRd==1&&len_Rd>0)//

begin

datout<=len_Rd+2; //55 len data

startRd<=2;//startRd<=2;

RDY<=1;

end

if(RDY==1&&len_Rd==0)//清零,防止触发后没有合适的数据,导致RDY一直为1,不停发送零

RDY<=0;

if(startRd==2)//if(startRd==2)

begin

case (type1)

3'h4://读取过零点位置数组 B

begin

if(rdaddr[0]==0) datout<=zeroB[rdaddr>>1][15:8];

if(rdaddr[0]==1) datout<=zeroB[rdaddr>>1][7:0];

end

3'h5://读取平均值数组B

datout<=averB[rdaddr];

3'h6://读取 非零数组B

datout<=memB[rdaddr];

default://reserve

datout<=0;

endcase

rdaddr<=rdaddr+1;

RDY<=1;

end

if((rdaddr>=len_Rd)&&(rdaddr!=0))//if(rdaddr>=len_Rd)//

begin

startRd<=0;

RDY<=0;

rdaddr<=0;

len_Rd<=0;

end

end

endmodule

主要占用资源的是以上模块,加上后Total Logic Elements由10%直接增加到94%,芯片型号是cyclone 4 E系列。

图中,如果不把typeA[2..0]连接到getvalue1,Total Logic Elements只用了10%,连接上后,Total Logic Elements直接飙到了94%,请问是哪里出了问题,还是getvalue1模块的问题,getvalue1中的代码有什么优化的方法可以减少Total Logic Elements的使用。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>