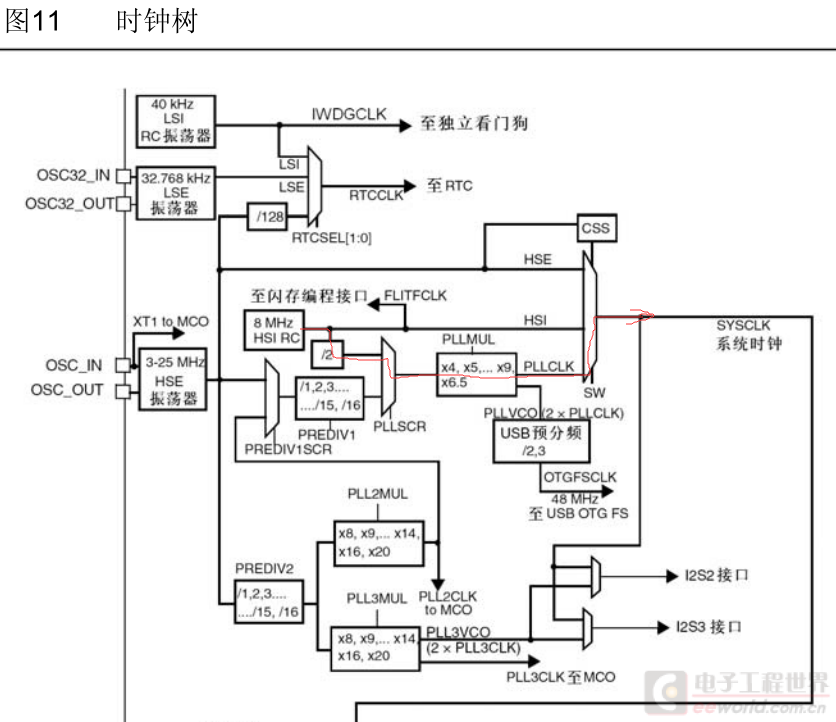

最近遇到一个问题很疑惑:1.查看STM32F103XXX参考手册的时钟树得SYSCLK最大为8/2*9=36MHz;

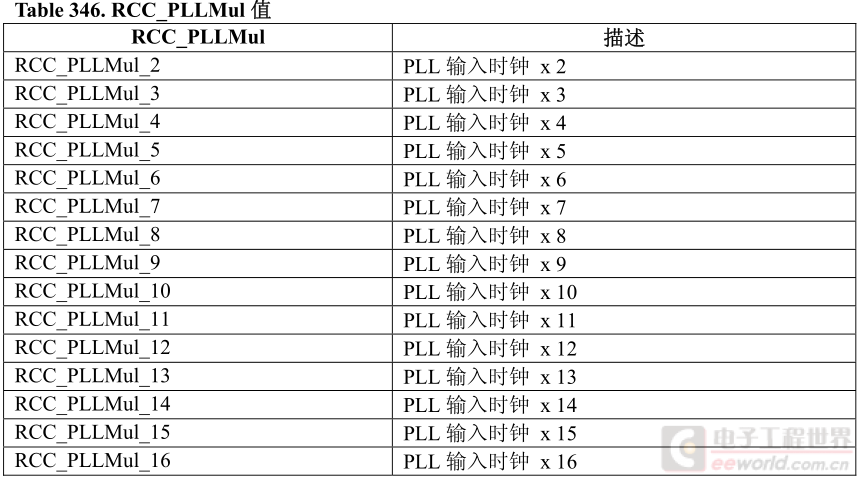

2.查看STM32_Library_Manual,15.2.6 函数void RCC_PLLConfig(u32 RCC_PLLSource, u32 RCC_PLLMul),其中RCC_PLLSource取值RCC_PLLSource_HSI_Div2,RCC_PLLMul取值范围:

得SYSCLK最大为8/2*16=64MHz;

网上查资料http://blog.sina.com.cn/s/blog_a5b8978f0101f39i.html却得到不同的时钟树:

请问STM32使用HSI时的最大SYSCLK到底是多少?

此帖出自小平头技术问答

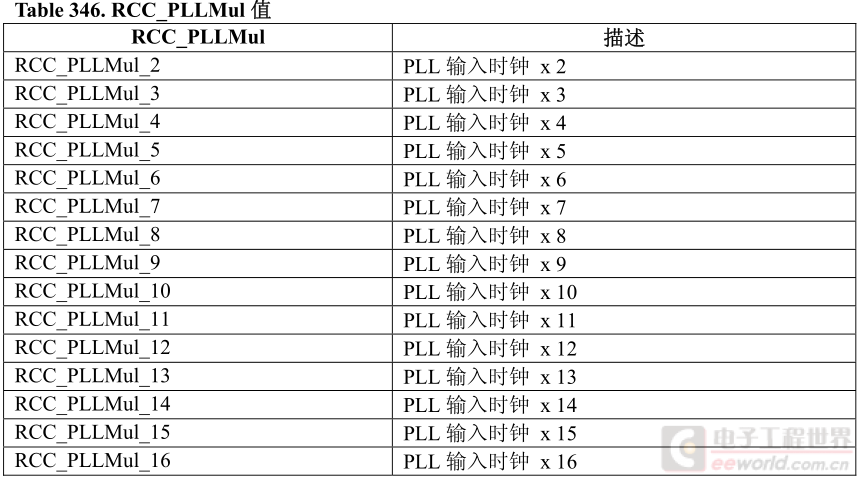

2.查看STM32_Library_Manual,15.2.6 函数void RCC_PLLConfig(u32 RCC_PLLSource, u32 RCC_PLLMul),其中RCC_PLLSource取值RCC_PLLSource_HSI_Div2,RCC_PLLMul取值范围:

得SYSCLK最大为8/2*16=64MHz;

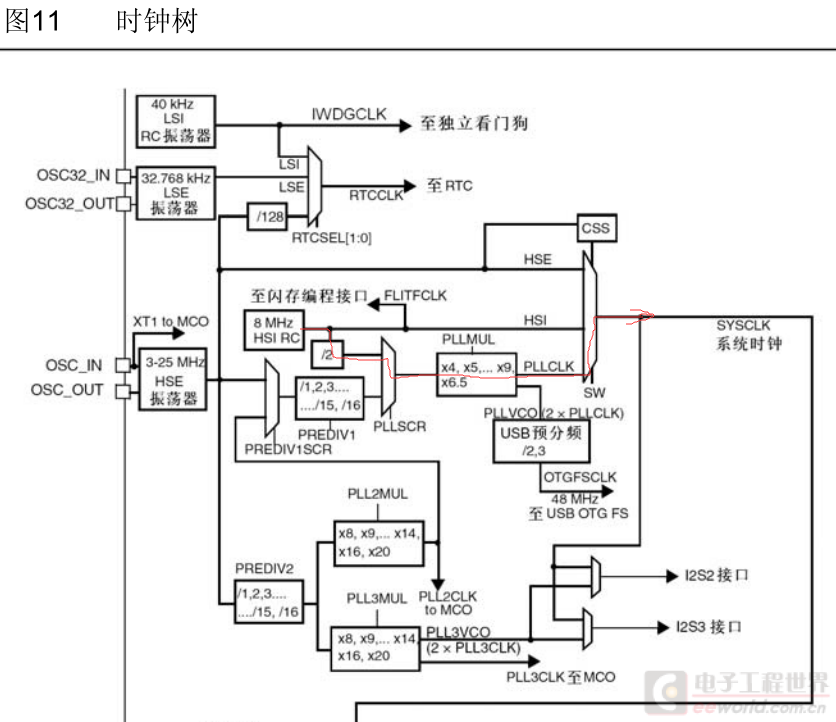

网上查资料http://blog.sina.com.cn/s/blog_a5b8978f0101f39i.html却得到不同的时钟树:

请问STM32使用HSI时的最大SYSCLK到底是多少?

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

时钟源我在标题里面说了是内振,如果用外振我就不会问这个问题了

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接

外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、

HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最

大不得超过72MHz。

一周热门 更多>