初学Quartus 2不久。根据这个原理图来写程序,单进程和双进程的。我写的程序似乎有错,可是不知道错在哪里,改了好多天了,仿真还是有错啊~ 还是搞不掂。唯有向各位请教了。帮我看看我的程序哪里有错,怎么改,谢谢了!

还是搞不掂。唯有向各位请教了。帮我看看我的程序哪里有错,怎么改,谢谢了!

还是搞不掂。唯有向各位请教了。帮我看看我的程序哪里有错,怎么改,谢谢了!

还是搞不掂。唯有向各位请教了。帮我看看我的程序哪里有错,怎么改,谢谢了!

-

这个是原理图

-

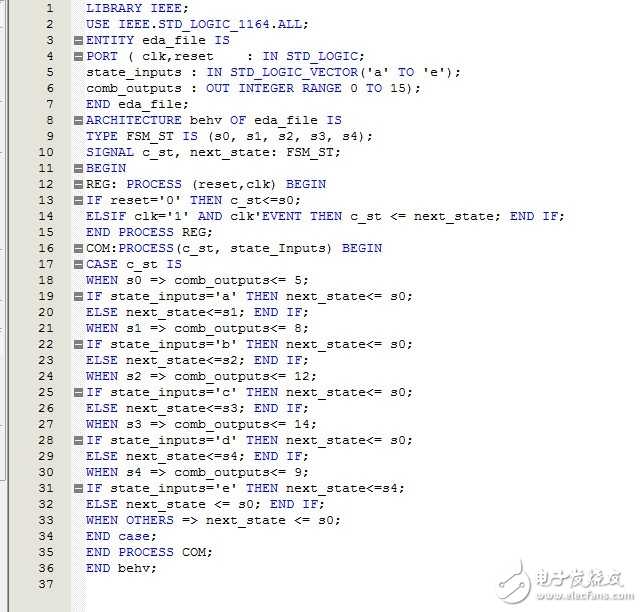

这是双进程的

-

这是单进程的

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY s_machine IS

PORT ( clk,reset : IN STD_LOGIC;

state_inputs : IN STD_LOGIC_VECTOR (0 TO 1);

comb_outputs : OUT INTEGER RANGE 0 TO 15 );

END s_machine;

ARCHITECTURE behv OF s_machine IS

TYPE FSM_ST IS (s0, s1, s2, s3); --数据类型定义,状态符号化

SIGNAL current_state, next_state: FSM_ST;--将现态和次态定义为新的数据类型

BEGIN

REG: PROCESS (reset,clk) --主控时序进程

BEGIN

IF reset = '1' THEN current_state <= s0;--检测异步复位信号

ELSIF clk='1' AND clk'EVENT THEN

current_state <= next_state;

END IF;

END PROCESS;

COM:PROCESS(current_state, state_Inputs) --主控组合进程

BEGIN

CASE current_state IS

WHEN s0 => comb_outputs<= 5;

IF state_inputs = "00" THEN next_state<=s0;

ELSE next_state<=s1;

END IF;

WHEN s1 => comb_outputs<= 8;

IF state_inputs = "00" THEN next_state<=s1;

ELSE next_state<=s2;

END IF;

WHEN s2 => comb_outputs<= 12;

IF state_inputs = "11" THEN next_state <= s0;

ELSE next_state <= s3;

END IF;

WHEN s3 => comb_outputs <= 14;

IF state_inputs = "11" THEN next_state <= s3;

ELSE next_state <= s0;

END IF;

END case;

END PROCESS;

END behv;

还是不行啊。似乎怎样改状态图都有问题,可是仿真却是没问题的!

NST没有读取...

状态图好像也错了

为什么输入是“00”和“11”的?我在编译的时候改成其他的就状态图就不正确了...

一周热门 更多>